Modbusͨ��Э���FPGAʵ��

O ����

�����ֳ�������һ��Ӧ���������ֳ������ֳ��豸֮�䣬�ֳ��豸�����װ��֮��ʵ��˫���С���ڵ�����ͨ�ŵļ�����ModbusЭ����ڵ㰲װ�����dz��࣬��װ�ĵ����鼰������ء�

���������FPGA�ɰ�����Ƕ�˷�����ר�ü������̺�Ƭ��RAM�ȣ�����FPGA�IJ����ԣ������ȽϿ��DSPоƬ��Ҫ����500���������ࡣ����FPGA�۸��½���������С������������ʵ��һ�����ɿ�ѡ����I��O���ܵ����������ˡ��ɼ���FPGA��Ƕ�����Ӧ��Խ��Խ������������

����ĿǰModbusЭ��ʵ�ַ�ʽ��Ϊ��Ƭ����PLC������FPGA�Ĺ㷺Ӧ�ã��о�Modbus�ֳ����ߵ�FPGA��������кܴ��ʵ�ü�ֵ��

1 Modbus����

����Modbus������·ϵͳ����ʹ�ò�ͬ�������ӿ�(RS 485��RS 232)���ϳ��õ���RS 485�����ƽӿڡ�Ϊ�����ͨ��ģ���ڹ�ҵӦ���еĿ������Ժ��ȶ��ԣ��ӿ�оƬ��FPGA����ģ��֮��Ӧ������ٹ�����и��룬�������˴�������·�ն˵��裬��������˫������Ϊͨ���ߵȡ�

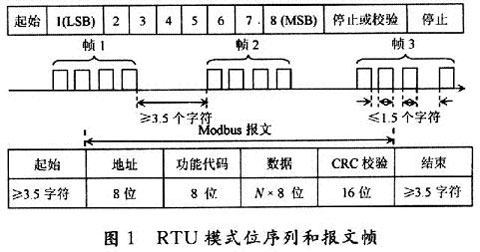

�����ڴ�����·�ϣ�Modbus RTU(Remote Terminal Unit)ģʽ������ÿ8��λ�ֽں�������4λʮ�������ַ�������ģʽ����Ҫ�ŵ��ǽϸߵ������ܶȣ�����ͬ�IJ������±�ASCIIģʽ�и��ߵ������ʡ�RTUģʽÿ���ֽ�(11λ)�ĸ�ʽ��ͼ1��ʾ��֧���桢ż����У�飬ʹ����У��ʱҪ��2��ֹͣλ��Modbus RTU֡�ϴ�Ϊ256B���ɷ����豸��Modbus���Ĺ���Ϊ������֪��ʼ�ͽ�����ǵ�֡������֡��ʱ������Ϊ3��5���ַ�ʱ��Ŀ��м�����֣���������֡�������������ַ������ͣ���������ַ�֮��Ŀ��м������1��5���ַ�ʱ�䣬����֡����Ϊ�����������սڵ㶪������ͼ1��ʾ��

������Ӧ�ò��ϣ�Modbus��һ������Ӧ��Э�飬�����ṩ������涨�ķ���������Modbus�����룺�����롢�û�������ͱ����룬����������ֻ�ù����룬����Ҫ��������(��Ȧ)���ʡ�16 b(�Ĵ���)���ʡ��ļ���¼���ʡ���Ϻ�������Ϣ���ʡ�

2 Modbus RTUͨ��Э��ӿ����

����2��1 �ӿڹ��ܼ�ģ�黮��

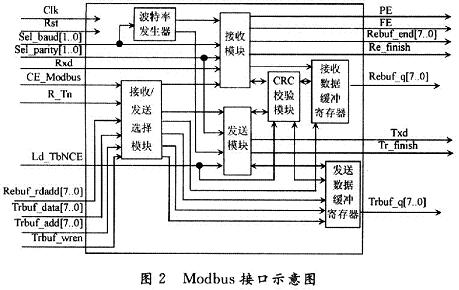

����Modbus RTU�ӿڿ�ͼ�����롢�������ʾ��ͼ��ͼ2��ʾ��

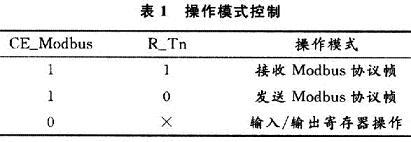

������ijһȷ������ʱ��Ƶ�ʡ�ͨ�Ų����ʺ���żУ�鷽ʽ�£�ͨ������CE_Modbus��R_Tn��״̬�����Կ��Ƹýӿ�ģ�鴦�ڽ���ModbusЭ��֡ģʽ������ModbusЭ��֡ģʽ�����룯����Ĵ�������ģʽ�����1��ʾ��

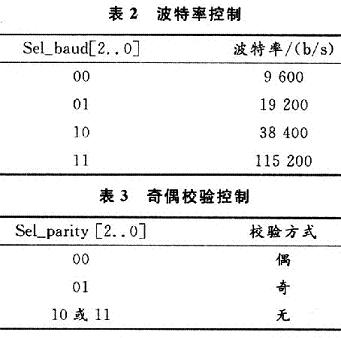

�������͵IJ����ʺ���żУ��λ�������2����3��ʾ������������źſ��ԴӶ˿������ӵ����뿪�أ�Ȼ�����ͨ�����ڲ��뿪���������Ƹ��豸��ż���벨���ʣ�Ҳ����ͨ���Ĵ������÷�ʽ���ơ�

����2��2 ���չ���

����(1)ϵͳ���ڽ���ModbusЭ��֡ģʽ��֮�������־λ�Ͷ�ʱ����Ȼ��������ʱ����������д����������ݣ������㶨ʱ�������û�м��������������Ҷ�ʱ����һ�μ�ʱ��3��5���ַ�ʱ�䣬��֡��ʼ��־��

����(2)�ѽ��յ��ĵ�һ���ַ�������ջ���Ĵ�����0x00��ַ(Э��֡�ϳ�Ϊ256 B���ʽ��ջ����СΪ256 B����ַΪ8 b)�����ѿ�ʼ���ձ�־��

����(3)�����յ�����ȷ�ַ����η�����ջ���Ĵ����У�����ַÿ�μ�1��ÿ������һ���ַ�֮�����㶨ʱ��������ڽ����ַ�ʱ��鵽��ʼ����(��ʼλû�г�������������Ӧbitʱ���һ��)����żУ�������֡����(ֹͣλΪO)���������ַ�������ͬ����ʼλ��

����(4)����������ַ�ʱ��������1��5���ַ�ʱ�䣬������֡��ʼ��־������һ�����յ����ַ�������ջ���Ĵ�����0x00��ַ���ټ�������(3)��

����(5)����û���ַ������Ҷ�ʱ���ڶ��μ�3��5���ַ�ʱ�䣬��Э��֡������ȫ��־��

����(6)�ѽ��ջ��������յ�������CRCУ�飬���У�鲻��ȷ����֡��ʼ��־��ת������(3)�������ȴ����գ�����ǻ��ڸýӿڵ���ModbusЭ���豸��һ��Ӧ���ó�ʱʱ�䣬�Ա������ȴ������У����ȷ����Re_finish����һ�����壬��Ϊ������һ����������·������ȷ��Mod-busЭ��֡��

��������֡����(ֹͣλΪ0)��־FE����żУ������־PE���Ϻ�һ�����յ����������ڽ��ջ������е�λ��Rebuf_end[7����O]�����Ⲣ�����룬����������Щ�˿ڱ��ã����������߱�ʾ��

����2��3 ���룯����Ĵ�������

�������ջ������ݼĴ����ͷ��ͻ������ݼĴ���������˫��RAMʵ�֣���ȼĴ���ʵ��Ҫ��ʡ�ܶ���Դ��Ϊ�˱�֤�����ǵIJ�����ԭ�ӵģ���Ϊ�˱���ͬʱ����ͬ��ִַ��д��������Ҫ��CE_Modbus�õ�ʱ���ⲿ�ſ��Զ���������Ĵ���ִ��д��������ʱ�ӿ��ڲ�����Խ��գ�����Ĵ���ִ���κζ�д������

����2��4 ������

����(1)�ڷ���ģʽʹ��֮ǰ��Ӧ�ȴ������룯����Ĵ���ģʽ��ͨ��Trbuf_data[7����0]��Trbuf_add[7����0]��Trbuf_wren�Ѵ����͵IJ�������λCRCУ���ModbusЭ��֡�ӵ�ַ0x00����д�뷢�ͻ���Ĵ����У�Ȼ��ʹ��Ld_TbNCE�ź�(һ��ʱ������)��ͬʱ���뷢�ͻ���Ĵ�����װ�Ϻ�һ�����ݵĵ�ַ��Ȼ��Ѹýӿ����ڷ���ModbusЭ��֡ģʽ��

����(2)����ģ���ȶԷ������ݻ���Ĵ����е���������CRC-16У�飬Ȼ��Ѽ������ý������λ��ǰ��λ�ں��˳�����ηŵ���Ld_TbNCE�ź�����ĵ�ַ����������ַλ�ô���

����(3)����ģ��ӷ������ݻ���Ĵ���Ox00��ʼ�����ζ������ݲ��������IJ����ʷ��ͳ�ȥ�����Ҫ����żУ�飬����������֮����ϼ������õ���żУ��λ���ͳ�ȥ��

����(4)��������Ϻ�һ�����ݼ�CRC-16�ĸ�8λ����֮��Tr_finish����һ�������ʾ������ϡ�

3 �ӿ�ģ��ʵ��

����3��1 �����ʷ�����

���������ʷ���������һ����Ƶ��������ϵͳʱ�ӷֱ�λʱ��(Tx_clk)��1��16λʱ��(RX_clkl6)������ϵͳ��ʱ�����ڿ��ܲ�ͬ��Ϊ��ģ���ͨ���ԣ���ģ����һ������(Generic)���������ַ�Ƶϵ����Ϊ�˱�֤ͬ����ƣ�������λʱ�Ӻ�1��16λʱ����Ϊ�����ź�����ʱ�ӵ������¿�������ģ�顣

����3��2 ����ģ��

��������ģ�������ͬ���˲�ģ�顢���ջ�ģ�顢���տ���ģ�顢����״̬�Ĵ���ģ�顢ʱ���־����ģ��ȡ�

����Modbus�������豸�������ڲ����ʱ���ϵģ�Ϊ�˱�������̬����Ҫ��ͨ���źŽ���FPGAʱͨ�����������ļĴ������첽�����źű������㹻��ʱ���ڱ���������Ч���Ӷ���֤��Ŀ��ʱ��������ڽ��ն�����Ϊ�����Ǵ��ڼ���������ȵ��źŲ���Ӧ�ñ������źţ������ڽ��ն˼����˲�ģ�飬�����㷨���£�����3�μ�Ϊ��(���)��ƽʱ���������ռĴ���д���(���)��ƽ������ԭ�����ĵ�ƽ������3��������ȵ��źű����ˡ���Ȼ��ͬ���˲�ģ��������5��ʱ�ӵ��ӳ٣�����������ʱ����ModbusЭ����˵���Ժ��ԡ�

�������ջ�ģ����һ���Ľ���UART����ģ�飬�乤���������£�

����(1)������ʼλʱ��������ȡ����λ��ͨ����λ���������˽�����λ�Ĵ���RSR�У�

����(2)�����е�����λ��ֹͣλ��������Ϻ���RDR�Ĵ�������־RDRFλΪ1��

����(3)���ֹͣλ����żУ��λ��������ִ�������ش����־λ��

����(4)���������������ȷ��RSR���������뵽�������ݼĴ���RDR�У���������־��

������Rxd_syn�Ͻ���ı������뱾�ص�λʱ�Ӳ���ͬ���ģ�Ϊ�˱�������ڴ����ʱ���ȡһЩλ����ÿ������ʱ�����16�Σ���ʱ��Rx_-clkl6��ÿ�������ز�����Ϊ�˱�֤�ϴ���жȣ�����������½���ÿ����ʱ���м���в����������ж���ʼλ�������Rxd_syn�����������λʱ��Ϊ�͵�ƽʱ�����ӵ�һ�μ��͵�ƽ֮��������9�μ�⣬���Rxd_synΪ�͵�ƽ�Ĵ������ڵ���8�Σ�����Ϊ��ʼλ��������ʱӦ������ʼλ�м������Rx_clkl6����֮��ÿ��16��Rx_clkl6ʱ��������14��15��16�������ص���ʱ�ֱ������Ȼ���3�β������ȡ����������ȵ�������Ϊ�����յ���ֵ���Ա�֤�������ݵ�ȷ�ԡ�8������λ�ɼ����֮����Sel_parity[1����O]�ź��ж��Ƿ���żУ�飬�����У��������Ե�9������λ������ͬ����3�β���ȡ������ֵͬ��Ϊ���յ�����żУ��λ��ͬʱ������żУ��������ֹͣλ(��������ʼλ����У��ʱΪ��9λ����У��ʱΪ��10λ)����ʱ��ͬ������3�β���������ֻҪ��1λΪ�߾���Ϊֹͣλ��ȷ��Ϊ�˼���״̬��������������ֹͣλ����ʱ�Ƚϼ���������żУ��λ�ͽ��յ�����żУ��λ�Ӷ��ж����������Ƿ���żУ��������ڽ��տ�����һ�����ȡǰһ�������ֽڲ�����RDRF�����Գ�����UART��ij���(overrun)�������ﲢû�г��֡�ͼ3Ϊ��QuaRTUs�������Դ���������������

����3��3 ����ģ��

��������ģ��������Ϳ���ģ�飬���ͻ�ģ�飬����״̬�Ĵ���ģ��ȡ�

�������ͻ�ģ���ǻ�����ͨUART����ԭ����ƣ��䷢�������£�

����(1)�ȴ�TDRE=��1�������ȴ��������ݼĴ���(TDR)Ϊ�գ����TDR������һ���ֽ����ݣ�����TDRE���㡣

����(2)���ݲ���������Sel_baud[1����0]��TDR������ݽ�����żУ����㡣

����(3)��TDR������ݷ��뷢����λ�Ĵ���TSR��1��8λ��TSR��Oλ����ʼλ(��O��)��TSR��9λ������żУ��λ����ֹͣλ(��1��)��

����(4)ͨ����TSR

����Ķ�:

- ...2012/03/19 11:00�����ڣͣ�����ԣãе��������ͨ�Žӿ�ʵ��

- ...2011/06/20 13:50��9~24VIN �� 1.8VOUT/1A �������� ��Module? ��Դ

- ...2011/06/17 15:31��4.5~28VIN �� 2.5VOUT/6A �������� ��Module? ��Դ

- ...2011/06/09 14:04������ EN55022B ���� 20~36VIN ��12VOUT/16A�����ࡢ������ ��Module? ��Դ

- ...2011/05/25 09:15������ ADSL MODEM �ڼ�ͥ�����Ӧ��С����

- ...2011/05/23 13:40��Single-Ended to Differential Converter with Gain of +2 and Common Mode Control

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������