Ӧ���ڱ�Ƶ��·��Ԥ�ÿ����Ƶ�����

��������DZ�Ƶ��·����Ҫʵ�ַ�ʽ��ֱ�Ӿ�����Ƶ�ijɰܡ���ͳ�������������������ģ���·ʵ�ֵģ��������ּ����ķ�չ��ȫ���������չ������ȫ��������Ļ�·����ȫ�����ֻ���ͨ�������ּ����������ֻ�·�˲�����ѹ�������Լ���Ƶ����ɣ�ȫ��������еķ�Ƶ��Ҫ��ģ��Ԥ���ҿɸ���ʵ����Ҫ���п����Ƶ[2]���������еĵ�·��������������Ҫ�������Ȳ���simuink ��FPGA ������Ӧ���ڱ�Ƶ��·�ı�ģ�����Ƶ����

����2. ��ģ�����Ƶ���Ĺ���ԭ��

������ģ��Ƶ���Ļ���ԭ��������һ�����Ϻ������ڷ�Ƶ�����У��������������Ԥ��ģ�Ƚϣ����������������Ԥ��ģһ��ʱ������������źţ�ǿ�ȼ�����������ϣ����״̬������ʼ״̬�������������տ�ŵͼȷ���ij������������ֱ���Ϻ�һ��״̬�����ɵ�ַ��ȷ���ĵ�N-1 ��״̬����ǿ�ȷ�Ƶ���ص���ʼ״̬[3]������ÿ��������Ӧ���ܵ��������ƺ����Ŀ��ƣ�����

����f—�������ɿ�ŵͼ�õ��Ŀ��ƺ���;

����F—ǿ�ȷ�Ƶ�������ϣ��״̬;

����T—���Ϻ���;

���������Ϻ���T = 1ʱ��F �������ã�P = f ����Ƶ�������������Ƶ;��T = 0��F �����ã�P = F ��ǿ�ȷ�Ƶ�����䵽��ϣ����״̬��

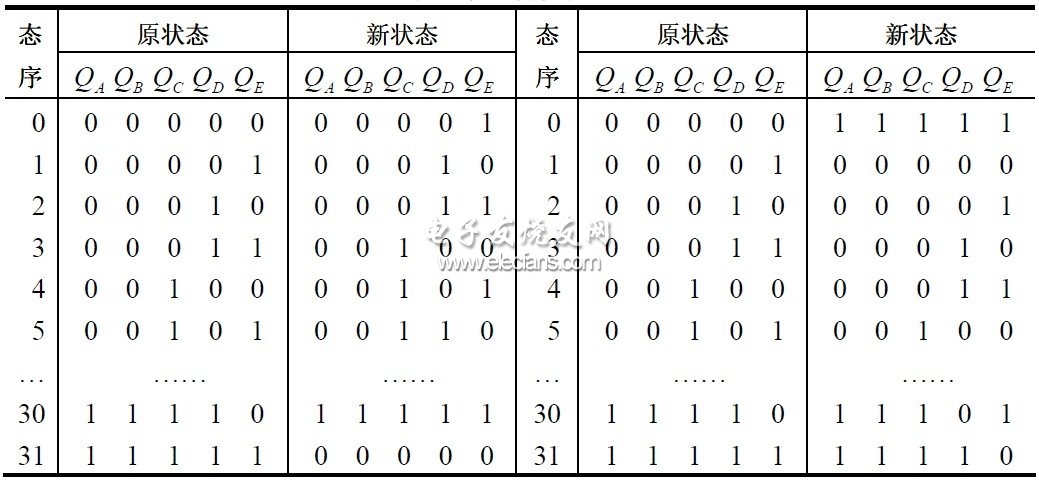

������1 ״̬ת����

����(ע����1 Ϊ״̬ת��ͼ��������벿��Ϊ������Ƶ��״̬ת�������Ұ벿��Ϊ�ݼ�״̬ת��������2 Ϊ����ֵ�����������ǰֵ�Ĺ�ϵ��)

������2 ����ֵ�����������ǰֵ�Ĺ�ϵ

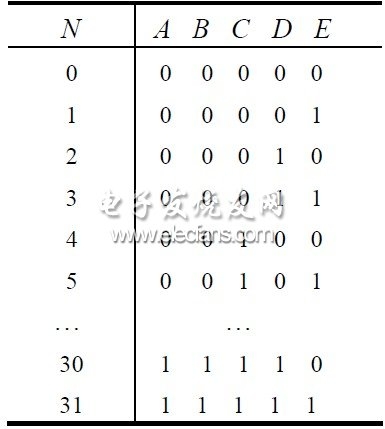

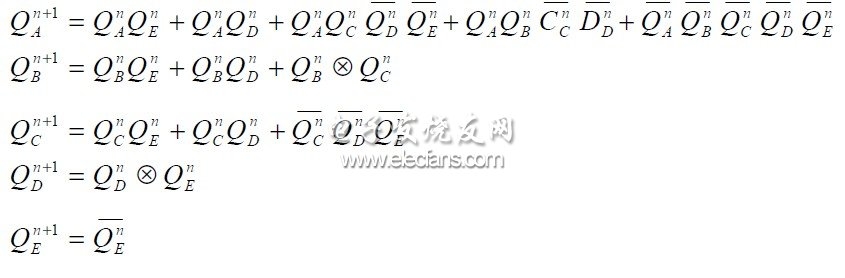

�����ӷ���Ƶ������������Ϊ��

����������Ƶ������������Ϊ��

���������������ܵ������źŵĿ��ƣ���I _ D�ź�Ϊ1ʱΪ������Ƶ������֮Ϊ�ݼ���Ƶ����

������������������������

����3. ����simulink�Ŀ����Ƶ�����

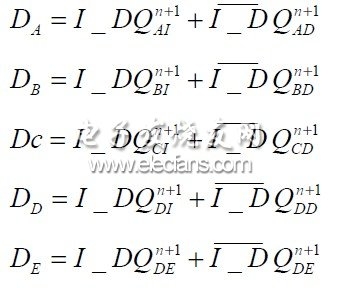

��������simulink ���������Ƶ��ģ�ͣ���ͼ1 ��ʾ����Ƶ�������弶D ������ʵ�֣���֮�Ա�Ҫ�Ŀ������������A��B��C��D��E Ϊ����ģֵ��I _ DΪ1 ʱ��Ƶ�������ڵ���ģʽ����I _ DΪ0ʱ��Ƶ�������ڵݼ�ģʽ�����Ϻ��������T������D������������ˣ���Ƶ���Ĺ���������ͼ2 ��ʾ����ͼ�п��Կ�����Ƶ���ܹ���Ԥ��ģ����ɵ�����ݼ���Ƶ�����ܡ�

ͼ1 �弶��Ƶ��

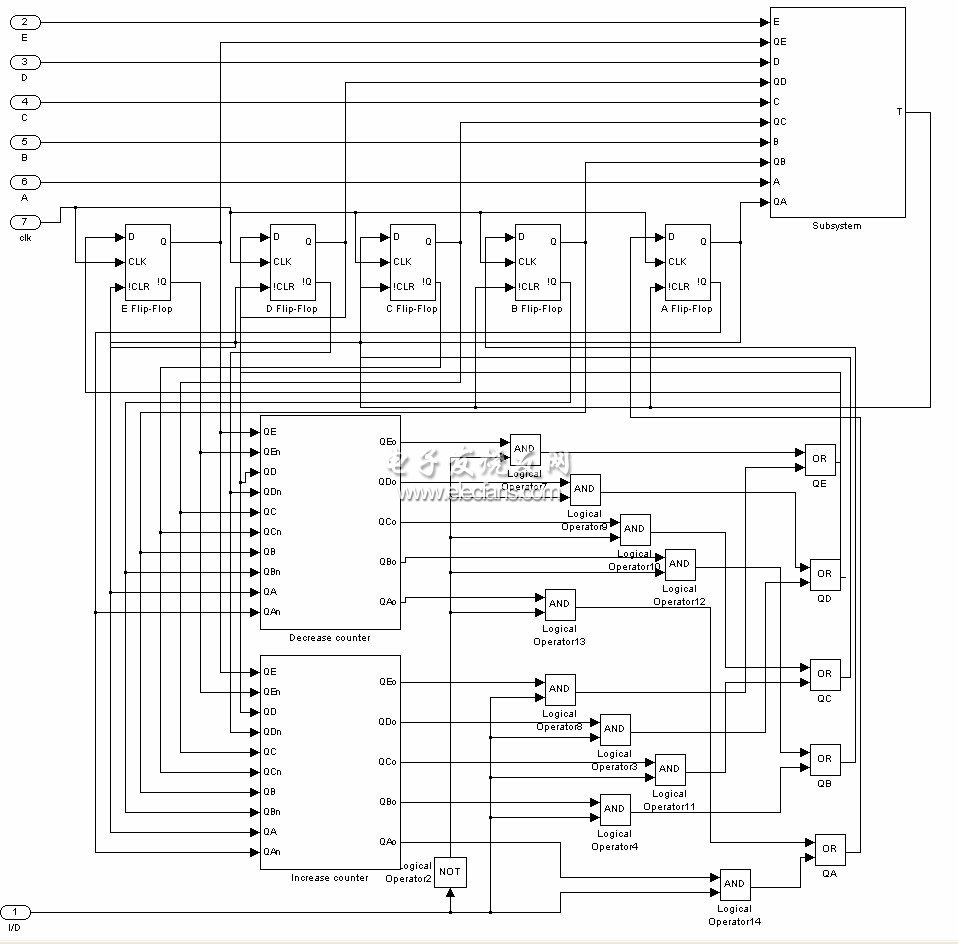

ͼ2 ��Ƶ���Ĺ������Ρ�

ͼ3 ��Ƶ���ķ��沨�Ρ�

����4. ����FPGA�Ŀ����Ƶ�����

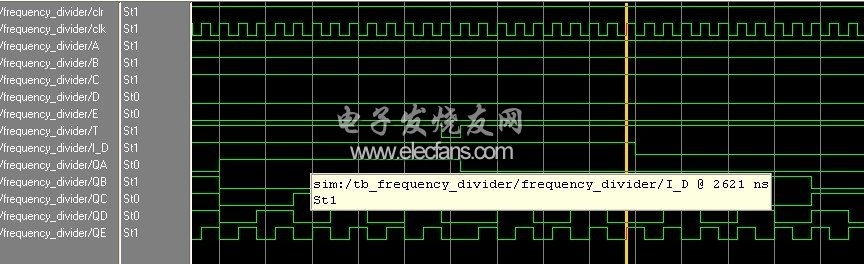

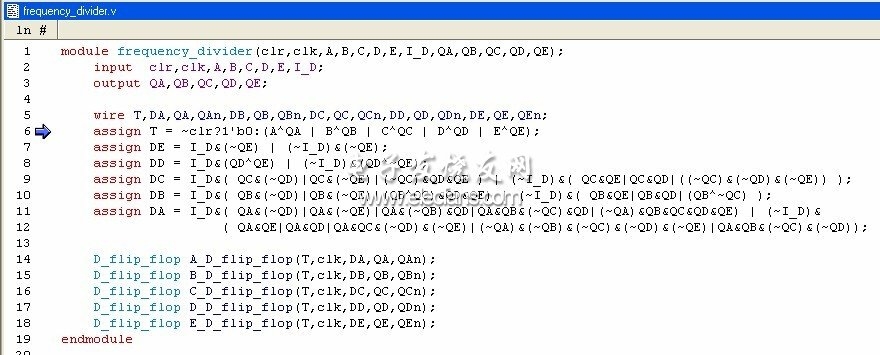

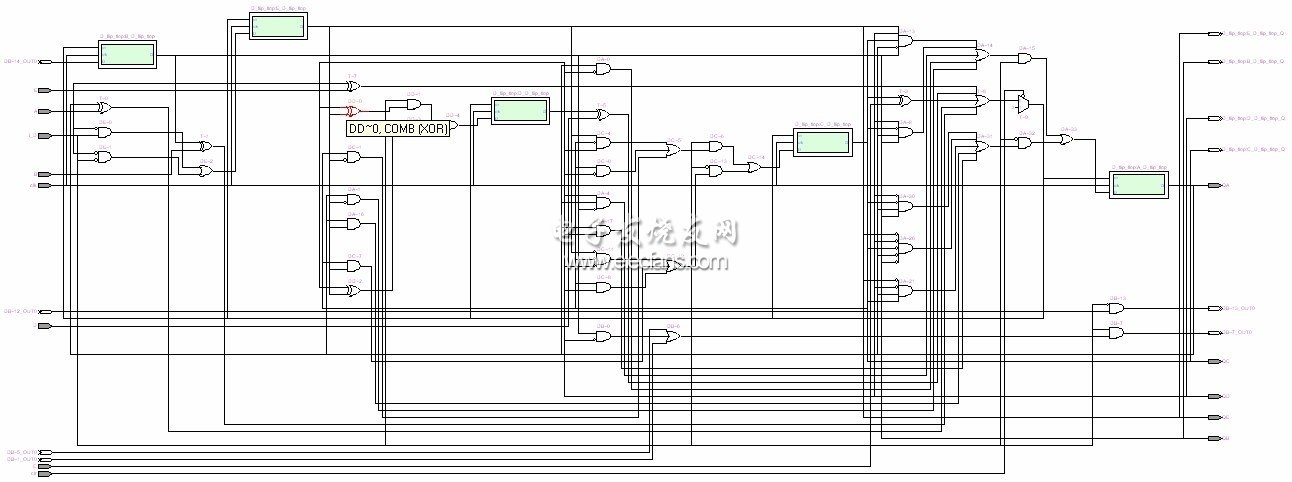

��������verilog ����ʵ���˿����Ƶ��������沨����ͼ3 ��ʾ����Ƶ�������Ԥ��ģ�Լ��������ݼ���Ƶ���ܡ���Ƶ����verilog ������ͼ4 ��ʾ���Ĵ������伶������ͼ5 ��ʾ��

ͼ4 ��Ƶ�����롣

ͼ5 �Ĵ������伶������

����5. �ܽ�

�������ķ����˱�ģ�����Ƶ���Ĺ���ԭ�������ֱ����simulink ��FPGA ʵ���˿����Ƶ����������������Ƶ���ܹ����Ԥ��ģ�������͵ݼ���Ƶ���ܣ��������Ҫ��

����Ķ�:

- ...2015/05/21 15:35����ɭ���뵼��Ӧ���ڿɴ���ҽ�Ƶİ뵼�巽��

- ...2013/06/13 16:46����ɭ���뵼��Ӧ���������Զ��յ��ĵ�Դ���������������Ԫ���ȷ���

- ...2012/09/17 13:57��UFSC��LabVIEW��NI CompactDAQӦ���ڳ���ͨ���������Ե���ѧ����������

- ...2012/08/13 13:52��UFSC��LabVIEW��NI CompactDAQӦ���ڳ���ͨ���������Ե���ѧ����������

- ...2012/03/13 13:33��ʸ���ֽⷨӦ���ڵشŵ���ϵͳ�е�������ȱ�ݷ���

- ...2012/03/13 13:23����������Ⱥ�㷨Ӧ����Բ����������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...�� ���ݲɼ��ն�ϵͳ�豸

- ...�� ���ǿƼ�̤��������

- ...�� ����˼® ���� AEC-Q100 ������֤������ϵ�в�Ʒ�ƻ�

- ...�� ����˼® ������������� �ѽ�ϵ��™ FPGA ��Ʒ �ѽ�ϵ�в�Ʒ���������� 1M ����Ԫ�� FPGA

- ...�� ����˼® ����Trion® Titanium ��̨���� (TSMC) 16�����սڵ���Ƭ

- ...�� TI��2019��ȫ����ѧ��������ƾ����佱�����ھ�����

- ...�� BlackBerry QNX��������ȫ����������ȫ�����Եȼ�(ASIL) ��D����֤

- ...�� ��������ѡ��BlackBerry������һ������