����DSP˫·��Ƶ�ź�ʵʱ����ϵͳ���

ժҪ ����TMS320C5509A��Ϊ���Ĵ�������������һ������DMA��϶�ͨ�����崮��McBSP��ɵ������źŲɼ�ϵͳ��ʵ�ַ������������������ݻ���ռ䣬�ɿ��ȶ���ʵ�����ݵ�ʵʱ���£����˫·�������źŵ�ʵʱ�ɼ��������ͷ��͡�������AICоƬ��DSP���ӵ����ú����ݽӿڵ���Ʒ���������CODEC��DSP֮�����ݴ���ij���ʾ��������֤������ϵͳ�ܹ��߾��ȡ����ȶ��������Ƶ�źŵIJɼ������ͷ������������ڸ��˱�Яʽ��Ƶͨ���豸������������

�ؼ��� DSP��DMA��TLV320AIC23B��ʵʱ�ɼ��������������

�ִ���Ƶ�źŴ�������ͨ����Ҫ�ɼ����������ݽ���ʵʱ��������Ŀ�Ӵ�����·�źŷ�չΪ������·�źš��������źŶ��ԣ�����Ԫ��ǿ����Ԫ�������Ϊ����ʶ���źŵĻ���������������Ƶ�źŴ���������Ҳ�Ӵ�ͳ��ģ����������ģת������չ��Ϊ��������ר��оƬ����ͳ�����ݲɼ�ϵͳ�Թ��ػ�����ͨ��Ƭ��Ϊ���ģ�����ϵͳ������ĸߣ�δ������������ʵʱ�����ͷ��͡���Ƶ�ʵʱ��������ϵͳ�����������������Ѹ�١��ȶ��Ըߡ��ɼ�������ʱС���ص㡣��ϵͳ����DSP�������ݴ�����DMA��McBSPʵ��˫·��Ƶ�źŵ�ʵʱ���вɼ����ͣ�����ʵ���ҽ������ݷ������㷨������Ż��������̵ȣ�Ҳ�����ڸ��˱�Яʽ��Ƶͨ���豸������������

1 Ӳ������

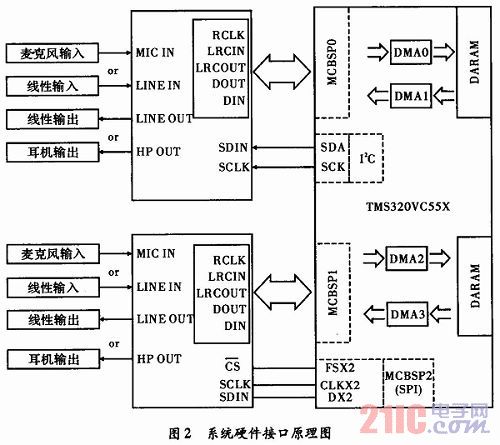

��ϵͳ��������Texas Instruments��˾TMS320VC55X����������̳���C54Xϵ�еķ�չ���ƣ����ġ��ͳɱ��������Ĺ����������ܹ��������������ܡ�������0��9 V����˵Ĺ��ʽ�Ϊ0��05W��MIPS�����ܿɴ�800 MIPS��������ͨ�š����������ȱ�ЯʽӦ���������ս�ṩ����Ч�Ľ����������TMS320VC5509AΪ������оƬ����3����ͨ�����崮�ڣ��ֱ�ΪMcBSP0��McBSP1��McBSP2��ÿ�����ڽ��պͷ�������ʹ�ö�����ʱ�ӣ�֧���������ͣ���ֱ�����ý�������źű������Ĺ�ҵ�ӿ��Լ�ADC��DAC�ӿ�ʵ�������ӣ�ͨ��CPU��DMA��16 bit�Ĵ�������ʵ��ͨ�ţ���DX���ŷ������ݣ�RX���Ž������ݡ�ͨ��ʱ�Ӻ�֡ͬ����CLKX��CLKR��FSX�Լ�FSR���������ơ�TMS320VC5509AоƬ�ṩ

6��ͨ��DMA���������ɶ�����CPU���4�����ӿڵ����ݴ��䡣ÿ��ͨ���ɴ�һ������Դ��ַ��ȡ���ݺ�д����һ���ڻ�Ŀ���ַ���ر�ָ��5509оƬ����64 kB˫����RAM����ṹ��8��4 kB×16λ�Ŀ���ɣ����������˿�ͬʱ���ʣ������ϵͳ�ٶȡ�

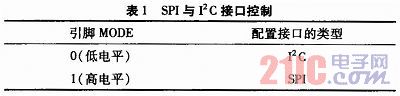

TLV320AIC23B��TI��˾�Ƴ���һ���������������Ƶ������������ö�������Ŵ�����֧��MIC��LINE��ѡһ�����뷽ʽ���������������пɱ�̵�������ڹ��ܡ�TLV320AIC23B��ģ����ת����(ADC)������ģת����(DAC)������оƬ�ڲ���������8��96 kHz�IJ������£��ṩ16 bit��20 bit��24 bit��32 bit�IJ������ݡ�ADC��DAC���������ȷֱ�ɴ�90 dB��100 dB��AIC23Bͨ����Χ���������ڲ��Ĵ������б�����ã������ýӿ�֧��SPI���߽ӿں�I2C���߽ӿڣ����1��ʾ��

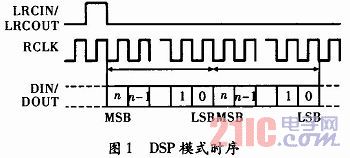

AIC23b���ݴ����ʽ֧�����ж�ģʽ�����ж�ģʽ��I2Cģʽ��DSPģʽ4�ַ�ʽ������DSPģʽר�����TI DSP��ơ�������оƬ��I��O��ѹ���ݣ��Ӷ�ʹ�ö��߿��������ӣ���ˣ�����DSP����ƵCodecоƬAIC23B������Ӳ��ϵͳ��һ������������źŴ���ϵͳ���������źŴ���ϵͳ�У�AIC23��ƵΪ12 MHz��A��D��D��Aת�����ij���Ƶ��Ϊ8 kHz��ģ����Ƶ�ź���LINEIN��MICIN���뵽��оƬ����Щ������Ҫͨ��McBSP1��AIC23��������ʵ�֡�ģ����Ƶ�ź�ͨ��A��Dת�����������������Ƶ�ӿڴ���DSP�Ĵ���McBSP0��������DSP����������ݣ��յ���������Ƶ�źž����롢D��Aת����HEADPHO��LINEOUT�������ϵͳ����DSPģʽ����ͼ1��ʾ��

I2C����Э������Philips��˾����������ʽ�������ߣ���������������������Χ�豸����Э���ѹ㷺��Ӧ��������ͨ��ϵͳӲ����·����С�

AIC23B���������Ľӿ���������һ���ǿ��ƿڣ���������MC23B�Ĺ�����������һ�������ݿڣ����ڴ���AIC23B��A��D��D��A���ݡ���I2C������AIC23B�Ŀ��ƿڽӿڣ���AIC23B�ĸ������ƼĴ����������á�McBSP�ķ��������ʱ�Ӿ���AIC23B�ṩ��

��DMAӦ���У����Ը���ÿ��ͨ����bit���ߵ͵����ȼ���ÿ��DMAͨ����ͬ���¼�ΪMCBSP�����շ��¼���ͬʱÿ��ͨ��ij���¼���ɺ����CPU����һ���жϡ��û����Ա�д�����ļĴ������ã���DMA�ڽ������ݴ���ʱ��ֻҪ�û�ʹ�ܸ�ͨ�����Ϳɽ����üĴ������Ƶ������Ĵ����С�����DMA֧���Զ���ʼ��ģʽ�������ڿ鴫������з������ƣ�����ʾ��ͼ��ͼ2��ʾ��

2 ����ϵͳ���

��������·��˷��������ݣ���·����������ݡ��ڴ˸���һ·�źŵĽ��մ��������̣���һ·�ź����˼·��ͬ��

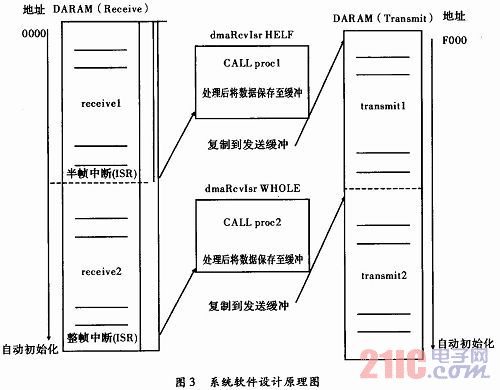

��DARAM�п��ٻ���ʹ�����Ԫ�����ݴ��������DMA������CPU�ķ�ʽ��CPUֻ���ڽ���DMA�����жϺ�����ݽ��д������������������ݿ�����DMA���ͻ��塣Ϊ��֤������������������ݶ�ʧ��DMA���ն˲��ð�֡�жϵķ�ʽ�������ݡ���������������У�����ѡ������������в���������������Ϊreceive1��receive2���ڱ�����������ݣ�ͬʱ���ٳ���������process1��process2�������г���receive������֡�жϣ�CPU��ȡreceive1�е����ݲ����临�Ƶ�process1�У����ô�������proc1����CPU��������źŴ���ʱ��DMA��������������receive2������ʱ������֡�жϣ�DMA�Զ���ʼ����receive1���ǡ�CPU��ʱ���ɽ�receive2�е����ݸ��Ƶ�process2�У����ô�������proc 2������receive��������£�����ʵ�ֳ���IJ�������С�

ÿ���жϷ�����������ʱ�����С�ڰ�֡�жϵļ��ʱ�䡣�˷������Ա�֤ϵͳ����ʱ�㹻С����ʹ�ø÷���ʱ���û���������Լ�����Ҫ��ƺ��ʵIJ���Ƶ�ʺͻ����������Ĵ�С��Ϊ���ϵͳ�ȶ��ԣ�ʵ����Ը���Ҫ������жϵ����ȼ���ϵͳ���������ͼ3��ʾ��

3 ������

ϵͳ����DSPVC5509��Ϊ���Ĵ����������������DSPƬ����Դ�����ö�����CPU��DMAʵ�������ݵ�ʵʱ�ɼ������Լ����ͣ�����������ռ���ʡ���ƵĿɸ��»�������������DMA����Ҫ����ұ��������ݶ�ʧ��ʵʱ���¼��������ݿռ���˷ѡ������ϵͳ���е��ġ��ȶ��Ըߵ��ص㣬���Ը����û������һ����չ��

����Ķ�:

- ...2012/04/23 12:22������DSP����Ƶ��Դ����ϵͳ���

- ...2012/03/06 19:39�����ڣģӣеĿ�����DZ任����

- ...2012/02/03 11:32������DSP��˫Ƶ������������Ӳ����·���

- ...2011/11/14 10:31������DC/DC�Ĵ������ѹ��·����

- ...2011/10/31 16:02������DSP�����״��źŲɼ�ϵͳ

- ...2011/10/28 10:28������DSP��OV6630��������ͼ��ɼ�ϵͳ

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������