����TDR (ʱ�����)����������ʱ

ժҪ������ʱ�����ʵ���ߣ����ø���ʾ������Դ̽ͷ������ʱ�Ĵ�ͳ�������ѻ��ȷ�������Щ̽ͷ��Ϊ�����ź�ͨ·��һ���֣�����ɱ����źŵ�ʧ�棬������̽ͷ������ֱ�������������ţ�������PCB (ӡˢ��·��)���߳��Ȳ�������ʱ������̽ͷλ�õ���һҪ�������Ѷ����ӵĹ��̡����Ľ������������TDR (ʱ�����)��������̽ͷ���ķ�������������ߴ�����ʱ�������ȡ�

��������

���Ļ�����������ǰ�

1.����TDR (ʱ�����)��С̽ͷ��TDRͨ�����������ź�ͨ·�������迹�仯�Ĺ�ϵ��TDRҲ�Dz���������2.ʱ����Ҫ���ߡ�

2.����ֱ��̽�⡣���ڼ��ص�ԭ����Դ̽ͷ��ʹ������ø��ӣ���������

3.����һ��ʵ����ʾ��һ���������Ľ���MAX9979Ϊ������оƬΪ�������ŵ��ӵ�·���ʺ���ATEϵͳ��оƬ�ڲ�������˫·��������������Դ�����Լ�������1Gbps���ϵĴ��Ƚ�����

�˴����ܵķ����������κθ���������

TDRԭ��

TDR���Է����У����ź�ͨ·��������źű��أ����۲��䷴���źš������ܹ�˵���ź�ͨ·���迹�Լ��迹�仯ʱ�ź���ʱ�ı仯��TDR���Եļ�ʾ��ͼ��ͼ1��ʾ:

ͼ1. TDRԭ����TDR�������ڷ���ϵ���ѣ����Ц� = (VREFLECTED/VINCIDENT)�����գ�ZO = �� �� (1 + ��)/(1 - ��)����ͼ1���Եõ�������Ҫ���

1.TDLY�����ǽ�Ҫ������PCB (ӡˢ��·��)������ʱ��

2.ZO�DZ���PCB���ߵ��迹��

������������

Ϊ�˲������뼶����ʱ����Ҫ�dz�������巢����������ʾ�����Լ�����̽ͷ������Ҳ�������þ���TDR�������ܵ�Tektronix® 8000 (ͼ2)ϵ��ʾ����(TDS8000��CSA8000��CSA8200)�����80E04 TDR����ģ��ʹ�á����IJ���MAX9979EVKIT (������)��Hewlett Packard 8082A���巢������TDS8000/80E04������ʾ��ͼ3��ʾΪMAX9979EVKIT���ֵ�·������ѡ��ʹ���κξ���TDR���ܵĸ���ʾ�������κθ��ٲ�����巢������ͬ���ܹ�������ƽ����

ͼ2. Tektronix TDS8000ϵ�о��в���ģʽ��ʾ����

ͼ3. MAX9979EVKIT (����)

�����н��������²�����

1.��PCB��SMA��Ե������DATA1/NDATA1��MAX9979 IC��������DATA1/NDATA1����ʱ����MAX9979��DUT1 (��������)���ͨ��SMA������J18����ʱ��

2.����DUT1�����CSA8000�IJ��Ե�����ʱ��

3.��DATA1/NDATA1������DUT1�����ͨ�����µ���CSA8000������ʱ��

4.�Ϻ���MAX9979��ʵ����ʱ��

DATA1/NDATA1���뽨ģ

�������Ƕ�TDR��Ӧ�Ƚ�����������������SPICE����������������ʱ��ģ�͡�Ȼ�����ǽ���������ʵ�ʲ������бȽϣ��μ�ͼ4��

ͼ4. ��Ч����ԭ��ͼ�ͽ��շ���ģ��

ͼ4ע�ͣ�

1.PCB�����趨Ϊ6in�����迹Ϊ65����ʵ���ϣ�����DATA1/NDATA1 PCB���ߵ���ʵ�迹�����������Ϊ50���������Ǵ�TDR����������ῴ����ֵΪ63����

2.NDATA1����˽����ء�����DATA1��NDATA1�Գƣ����Ҿ���MAX9979���ŵij�����ͬ�����Խ�����DATA1��PCB���ߡ�

3.���źŷ�������12in���½��н�ģ����ʵ�ʴ�����ʱ����֤��������Ҫ��һ��ģ��

DATA1/NDATA1�����

ͼ5��ʾΪTPv3��SPICE���沨�Ρ�

ͼ5. ͼ4��ʾģ�͵�SPICE����(�ڵ�TPv3)����MAX9979EVKIT DATA1����ɼ��������ݡ�

��ͼ5���ݿ��Եó����¼�����ۣ�

1.�����ź�Ϊ��Ծ��������η����У���Ծ����Ϊ0.5V���Դ�ģ��CSA8000������TDR�źš�

2.ʱ�����ģ���в�ͬ��Ԫ����ʱ��

a.��1����ʾ��������12in���¡���ʱ��ԼΪ3ns����ʵ����ʱ��������ʵ�ʵ�����ʱΪ1.5ns��

b.��2����ʾDATA1 PCB���ߡ���ʱ��ԼΪ2ns��PCB��ʱΪ��ֵ��һ�룬��1ns��

c.������ʱΪ����ͨ��DATA1 PCB���ߵķ��䡣

3.Y�ᷴӳ�˲�ͬԪ�����迹����λΪ���أ���ת��Ϊ�迹��

4.X��Ϊ���������Ծ�ź���ɵ�ģ���źŷ��䣬����ͼ1���źŽ��бȽϡ���Щ�źŵij��ȴ���ͨ����ͬԪ������ʱ��

MAX9979�Ĵ�����ʱ����

������������������д�����ʱ������

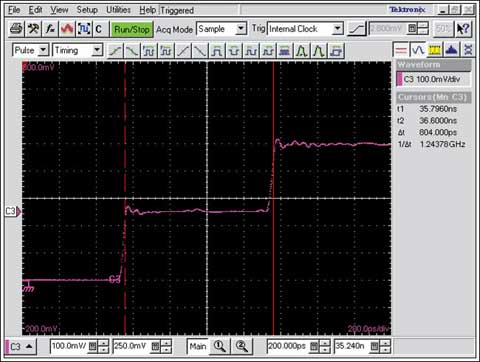

��1������������DUT1�ڵ㵽CSA8000��ֱ�����2in��SMA���µ���ʱ(ͼ6)��

ͼ6. 2in SMA���µ�CSA8000 TDR

����ʱ��

1.��2in��SMA-SMA����������80E04 TDRģ���һ·���룬��һ�˱��ֿ�·��

2.����TDR�������˵����в�����

3.ע�⣬�⿴��������ͼ1�еġ���·��ʾ�����˴���õ���ʱΪ804ps�������������ĵ�����ʱ�����Ե�����ʱΪ402ps��

4.����ע����ǣ���2����Ծʵ��Ϊ�����͵ײ�֮���һ�롣����TDRԭ������ʾ2in���ȵ���ʵ���迹Ϊ50����

5.����2in���������Dz�����ʱ��ͨ·֮һ��

��2��������DATA1�����źŵ�PCB������ʱ/�迹��

ͼ7. DATA1 PCB TDR�迹����

�Ӹ����ݿ��Ի�����¼�����Ϣ��

1.ͼ7��ͼ5�еķ���������ͬ��֤����ģ�͵�ȷ�ԡ�

2.������ڲ�����·�迹����1����ԾΪ49.7��������CSA8000���¡������ǵ�Ԥ�ڽ��һ�¡�

3.�ڶ������ʾ97.8����ΪMAX9979�ڲ�DATA1/NDATA1���˵�100������(�μ�ͼ4)�������ǵ�Ԥ�ڽ��һ�¡�

4.��2����Ծ�迹����50������һ��ΪDATA1 PCB�迹����ԼΪ63��������ζ��DATA1��NDATA1��PCB���߲���������ϣ����50����

5.���ֵΪ150�����Ƕ����50�����º�100�����裬ֻ�����ڵ�3�����䡣

�ò������Լ�Ϊ��

1.��12in SMA���µ�һ��������CSA8000����������һ��������MAX9979EVKIT��DATA1 SMA������������

2.��NDATA1��SMA������ͨ��SMA�ӵأ���ͼ4���Կ�����һ�㡣12in SMA���µij�������ʱ�����أ���Ӧ�����̡ܶ�

3.�����MAX9979EVKIT���硣�ò�����Ժ��ӵ���·���ϵ�MAX9979���У�������Ҫ�ϵ硣��Щ�û���ϲ��ʹ��û�к��������ĵ�·����в������Ͽ�MAX9979��������������3����Ծ�źţ�����ͼ1��ʾ��·״̬�����������£�ʵ��ʱ����������ͬ��

ͼ8. ������ͼ7��ͬ����Ϊ��չ��IJ��Σ�������ʱ��

ͼ8��ʾ��������2����Ծ��DATA1 PCB������ʱ��ע�⣺

1. ��1����ԾΪ���£����Ƕ�����ʱ��������Ȥ��

2.����ֵΪ1.39ns��PCB��ʱΪ��ֵ��һ�룬��Ϊ0.695ns����һ��ʱȷʵ����ģ�͵���ʱ�������ǽ�����ģ������ʱ���ԱȽϡ�

3.�������źŵ���б�ؽ��С���Щ��б�ش�����·��SMA��MAX9979 DATA1���ŵĵ���ЧӦ����ˣ�����Щ��б��֮����в����ܹ�ȷ�����Խ��������SMA��PIN��ʱ������ע����ǣ������д����壺����SMA���������·��֮��ĵ�в����ġ��ɴˣ���Ҫ����֮ǰ���в�������ȷ����ȡ�����ĵ�·����ʱ����һ����TDR����������ͻ����Щ���ݺ͵����ɵ���б�غ��塣

��3��������DUT1����źŵ�PCB������ʱ/�迹��

ͼ9. DUT1 PCB TDR��ʱ���迹����

ͼ9��ʾʾ���������Dz�����ͼ7��ͼ8��ͬ�����ò����ġ��������ڲ���һ��2in��SMA��������CSA8000 80E04ģ��MAX9979EVKIT��DUT1 SMA��ע�⣺

1.��1����Ծ��ʾ2in���¡�TDR�ź�Ϊ0.5V����1����ԾΪ250mV��˵�����ǵ��µ��迹Ϊ50������Ԥ�����һ�¡�

2.DUT1��ʱ����������б��֮����в����õ��ģ�������DATA1����˵����ͬ��Ȼ������Ҫע����ǣ���Щ��б��֮��ĵ�ƽͬ��Ϊ50������ֵ

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������