Lattice�ͳɱ�������FPGAΪCORDICӦ���ṩ�������ƽ̨

����˼�뵼�幫˾Ron Warner, Cort Lansenderfer

����

���ŵͳɱ�������FPGA�ij��֣������źŴ���Ӧ�ö����ܵ�Ҫ���������ӣ����ഫͳ������ʵ�ֵĽ���������ڸ����ת�Ƶ���Ӳ��Ϊ���ĵĽ��������������ͨ�š��������ߵ缼����ҽ��ͼ�������/�״��Ӧ���ںܴ�̶������������źŴ����ģ���������Ҫ��һ����Ҫ������CORDIC��CORDIC��������ת���ּ����Coordinate Rotation DIgital Computer����һ�ּ��ӳ˷��ĵ��������㷨������ؼ�������Ӳ���ĸ����ԡ�����ϵͳ�����Ա���ԣ�����һ�����˵�ѡ����Ϊ���ݶ���һ���źŴ�������������������ܵ�Ҫ�����Ǽ���������ƽ����̵ijɱ����ĵ���ս������������CORDIC�㷨���Լ��ÿɱ����������ʵ�ֵ������

CORDIC���ܵĸ���

����FPGAԽ��Խ�㷺��Ӧ��������ͨ��ϵͳ��FPGA֧���źŴ����Ĺ���ҲԽ��Խ�ࡣ������������˵�������źŴ����������������Ǻ������Ӹ�������˵��һϵ��ʸ������ת��Ϊ����Ч����Ӳ����ʵ����Щ���ܣ������ҵ�������淶��ʽ��صĹ��и����Եķ�����CORDIC�㷨������չ�㷨��ʸ����ת����һϵ�е���λ�ͼӷ��������FPGA�ڵĽṹ��Ԫ����֧���������㷨�ġ��ڱ����У�����Ҫ����CORDIC�㷨���Լ����������֧��������ͨ��ϵͳ��ص��ִ����Ǻ�����

��20����50���������CORDIC�㷨�ͱ�������֪���ϳ������ڸ�����ѧӦ�á�����ʱ���������ڸ��ֻ���Ӳ����������ʵ���˸��㷨������FPGA�����IJ��Ͻ�����������Ѱ�Ҹ��õ����ÿɱ��Ӳ������������ǵģ����Եĺ�˫���߹��ܵ�ʱ�̡������ע���ص���CORDIC����������Ӧ���в�������ν��Բ������ϵͳ��������Ǻ��������������������������Խ����ʱ���Ӹ�������˵CORDIC�ǻ���ʸ����ת�ģ���ͼ1��ʾ��

ͼ1

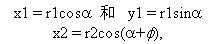

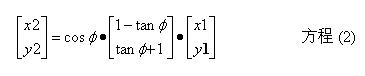

��r1Ϊԭʼʸ��������ϣ����ʸ����ת�������ʸ��r2��λ��(x2,y2)���ڵ�λԲ(|r1| = |r2|)������һЩ���������Ǻ��ʽ�����Ƕ�����תʸ��R1��ʸ��R2�Ľ���λ��Ϊ��

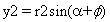

Ȼ�����û������Ǻ��ʽ�� X2���Ա�ʾΪ

�������

���ǿ��������Ƶ��滻�õ�

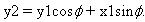

����ͨ����ΪGivens��ת��ͨ�þ�����ת��ʽ���������ڿ��Ա���ʸ��R1��R2֮��Ĺ�ϵ��

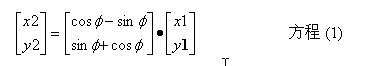

���������ṩ���ڶ�άƽ����һ�ּ�ʸ����ת��������������cosf�����ǿ�����д����(1)Ϊ��

����(2) �ṩ��һЩʸ����ת�����ʡ����ǿ��Կ�����R1��R2��ʸ����תֻȡ����ԭ���ͽ���ʸ��λ��֮��ļнǣ���ʾΪһ�����������Ļ���ԭ��ʸ����ÿ�������ĺͻ��߲���ԽǶȵ����У�����Ƕ�λ��ԭ����ʸ����Ҫ���ʸ��λ��֮�䡣�������Ҫ��һ�����������ת��Ϊһϵ�������ĸ�С��ת���ȷ�˵qiȡ��������ת�����ǿ��Զ�����ת���ܺ�Ϊ��

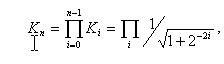

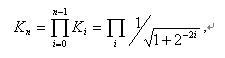

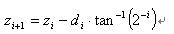

�õ�������i��ʾ��Ҫ��ľ��ȡ�Ϊ�˷���Ӳ����ʵ�֣����Ƕ��������ת�DZ�ʾΪ2���ݣ���tanfi = +/-2-i�����⣬��ת�Ƕȿ��������Ļ��߸���; ��ˣ�����������һ������di Î{1, -1} �Լ�ס��ת�ķ������ǽǶ�����ʱ��ʹ���˱���d������ÿ�ε������Ƕ�����������һ����صij߶����ӡ�ͨ�����еĵ������Զ���߶�����Ϊ��

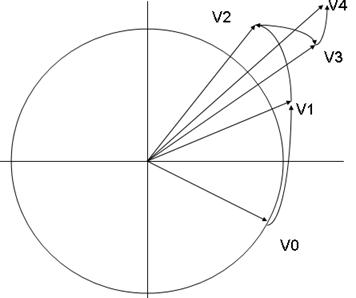

���ŵ������������ӣ����ӽ�0.6073��ͼ2�ṩ��CORDIC������Ӱ���ͼ�α�ʾ����ʼʸ��ΪV0 ������ϣ����ת�����յ�ʸ��V4��ע��ͨ��ÿһ�ε������ܵ���ת�Ƕ�����ε������ӵģ�ÿ�����������ĽǶ������ǰ�ĽǶȼ�С�ˣ��㷨������������Ҫ��ʸ��λ�á����ݾ���Ҫ�����Ƕ�̬���ɳ߶�����Ҫ�������Լش洢��Ӳ���в�����յļ�������ϵ��һ��

ͼ2

Ϊ����֤������ͨ��ÿһ�ε�����������Ҫ�����ۻ��������Ƕȣ�������Ҫ������һ���������Ա��������������ڼ��ۻ��������Ƕ�ֵ��

�ڡ� N ���ε���֮�����ۻ��ĽǶȿ��Զ���Ϊ��

���Կ�����zn������ʼ�Ǻ��ۻ���֮��IJ��Ӧ��ע����Ƕȶ����ڡ�xi�� �� ��yi��ֵ��ֻ������2-i �ĵ�������ֵ�ķ�����ֵ�����ÿһ��������ת�ĽǶ������ȵ�֪�ģ�ֵ������Ӳ����洢��FPGA�е�ijЩ���͵Ŀɶ��洢���С������ͼ����˽Ƕȼ���ĸ����ԣ�ֻҪ�������ǵĽǶ��ۼ������в��ҡ�Ӧ��ָ�������ø������ת��С�ĽǶȿ��Դﵽ���Ӽ����С�������뿼�Ǵ洢����Ҫ������ܵ�Ȩ�⡣

ȷ������

ʹ��CORDIC���������������ķ�����ʸ��ģʽ����תģʽ�������ַ������������Ĵ����������������˿�ʵ�ֵ��������ܡ��������CORDIC�㷨���ǻ���һЩ����ˣ�ֻ�ܹ��ƾ��ȣ���Ҫ�ǽ�Сλ����λ���Լ������������ڿɱ����������ʵ��CORDIC���ŵ�֮һ�Ǻ���������Щ����������������ľ��ȡ�

�����������ۣ�CORDIC�����ӵĹ��ܼ���һϵ����λ�ͼ�/���IJ�����������FPGA�ڵĵ���CORDIC����ʱ��������Ҫ����Ӳ���ܹ����ڴ�����ִ���FPGA�У���������������ֱ������Ĵ���������Ԫ����ˣ����ǿ��Լ��������·���������ӳ٣���Ϊ�ӷ���/��������ʱ��һ���֡�����ʵ����λ����ʱ����Ϊ������FPGA�ṹ�еĹ���ģ�飬�Լӷ���/����������ʱ����Ϊ����ͬ����ʱ�����Ǵ���ʵ��CORDIC�����⣬CORDIC��������FPGA���ṩ�IJ����ԡ�ÿһ�εIJ�������λ���Dz������ģ���ˣ��ϴ��ʱ���ٶ����Ƶ����������ܵ�����������n����n�ǵ������������ܺ�����Ƶ�����Ҫn���������ܵ���������һ��������Ȩ�⣬��ȡ���ڽϺ�ϵͳ����Ҫ����Ϊһ�����ӣ���������ʩ���ܵ�Ӧ���ںܴ�̶���ȡ��������Ƶ�����Ƶ��ʵ�֣��Լ���ѡ��ʵ��Ӳ���ܹ��ķ�������TDM�Ա�ר�õ����� �����⣬�ɱ���������������Ϊ��Ӧ������ṩ���������ƵĹ��ܡ�

�ܽ�

��Ȼ��CORDIC�㷨���˺ܺõ����⣬����Ӳ����ʵ�ֻ��ǽϽ��ŷ�չ�������¡�Ȼ�������������Ա��ͼƽ���������Ӧ�õijɱ������ܵ�Ŀ�꣬��ܿ��ܻ���һ���������е����ơ�����������������CORDIC�㷨����Եͳɱ�FPGAʱ�����������źŴ�����Ӧ�ã���Ϊϵͳ�����Ա�ṩ��һ�����ġ���Լ�ɱ��ĸ������ܵ�ѡ��

����Ķ�:

- ...2011/06/08 15:28��Fully Isolated AC Power and Current Monitor

- ...2011/06/08 15:27��Isolated Current and Voltage Monitor

- ...2011/06/08 15:27��Kelvin-Sensed Temperature Sensor Amplifier for �C50��C to 150��C Platinum RTD from 10V Refrence

- ...2011/05/30 10:53��Overvoltage Regulator with Low Battery Detection and Output Keep Alive During Shutdown

- ...2011/05/30 10:53��Paralleled Voltage Regulators with Balanced Load Sharing

- ...2011/05/30 10:53��Piezoelectric 3.3V Power Supply with LDO Post Regulator for Reduced Output Ripple

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������