����FPGA��ƺ��յ���ϵͳ

���Ľ�����һ�ֻ����ֳ��ɱ�������� (FPGA) ���ĵ�ʵʩ�������Ƚ����ִ����յ�����Ʒ�����

��������ж�������,��������������������Ʒ��ա�����ɶȡ���С����������ĺ���߹���ƽ����� ʱ��(MTBF)��,�������û���ԭ����ϵͳת�Ƶ��������MIL-STD-1553 ���г����������������ƶ��������� ;��ʵ��,ijЩ�ͻ��Ѿ������������ʵʩ�е������١�

MIL-STD-1553 ���Ĵ����˶��ֺô�,�������ų������ ASIC ��ͳ��FPGA �м���һ��֪ʶ��Ȩ����,�ͻ����һ�����ڲ�ͬ������,����Ϊһ���dz�רҵ�ĸ���ϵͳ����Ϊ��ǿ MIL-STD-1553 ������ṩ��ǧ���ѷ�Ļ��ᡣ

ϵͳ������ٵ�����

���ھ�����ѹ���ͶԽϼ�ս��������ֹ������,���ú��յ��ӴӼ��������豸��չ�������ÿ�����λ����������ٶȽ�����Ϣ�ĸ�����ϵͳ���硣��Ҳ�����˱���˷�������������⣨����1����

��Ҫ������ܵľ��������,ÿ����ƶ�Ҫ���ٿռ䡢���ĺ�����,������ЩҪ��������Ҫ������Ҫ��ֱ��������оƬ����,��һоƬ�����С�������忨��Ҫ ��Ҳ�ή��,�Ӷ������˶Է�װ��ǡ��̶�Ԫ������ȴ���������ǵ�Դ��Ҫ��ͬ��,ÿ������һ�����,��������һЩ�������ϵĻ��ᡣ����оƬ��������Ʊ�Ȼ �����ڻ�����Щ���⡣

���������� MIL-STD-1553 ���ʵʩ�������Ŀ�����ٵ���һ�����⡣ÿ�������������������ϴ���������ṩ,���������ڲ�����С��רҵ��Ӧ��,�������ŷ����ķ��ա���һ��Դ���� �����������ű������ķ���,���и����ڼ۸�������,�ر�����Щ��ԭ����Ŀ�̳е����,��������Ϊ���ԡ������Ѿ������ϵͳ,�������漰�Ĵ��۹���, Ӧ�����������ڷ�����������¶�ϵͳ������֤��

��ϵͳ�ܹ�ʦָ��һ��ϵͳ���ʱ,��Ȼ����ڼܹ�����ȷʵ�ֵ�ij�ַ��ա�һ���� �����͵������ǣ���������ƹ����л�ܹ�ȷ���ܾ�֮�����ڼ��ɽΣ�,��֪�����������仯����Щ�仯һ�㶼�����ӶԼܹ���Ҫ��,�����һЩ������Ƶij� ������,�磺����㹻��������ṩ��ֵĴ��������𣿹�����Ӳ��������֮���Ƿ������Ч�Ҹ�Ч�ؽ��������֣��ܴﵽ�ؼ�ʱ��Ҫ����

����״����,��ѡ���ļܹ�Ӧ����ǿ��Ӧ�����,�����ڳ�ʼ����ξͽ����ս����ϵ�,�����ṩ��һ������ϵͳ����ʱ�䷢չ��ƽ̨��

����������,һ�� MIL-STD-1553 ���ʦ���Բ��ô�ͳ�ļ���,ʹ���ж����Դ�� COTS ����������Щ���⡣�����ɴ����г��ṩ��������Լ۱��������Ե����ơ�

MIL-STD-1553 ���

�뿴һ�����ݴ���·��,��ͼ 1 �е� MIL-STD-1553 ���߽ṹ��MIL-STD-1553 ��һ�ֶ����������ߵĵ��Ӻ�Э���ص�ľ��ñ�����Ϊһ���ھ��ú���������㷺Ӧ�ó��� 25 ��֮�õ�����,���ҷ��� MIL-STD-1553 ��,������1Mbit/s�����ʸ߶Ⱦ�ȷ����Ϊ�ɿ��ش������ݡ�

���� MIL-STD-1553 ���Ĺ涨,���߽ṹ��������ͬ��Ӳ����ɣ�

�� ���߿������������߿�������������Ψһ���������������Ϸ�������,����������������������������Ӳ���豸�����ͬʱ�м����ն˿���ʵ�����߿������Ĺ���,ͬһʱ����ֻ����һ�����ڻ״̬��

�� ����������������������һ�����Լ����������Ϣ�������նˡ����������ڷ��в��Լ�¼�����й�����ϡ�ά����¼���������,ͬ ʱ������Ϊһ���������߿�����,�����㹻����Ϣ���Խ������߿�������Ȼ��,����������һ���������豸,�����ܱ�����������Ϣ��״̬��

�� Զ���նˡ���ÿ��Զ���ն˶��������������ߺ���ϵͳ�䴫������������ĵ���������֧�����м�������� MIL-STD-1553,��ϵͳ�������������ݵķ����ߺͽ����ߡ���Щ�ն˲�����Ϊ���߿���������������ʹ�á�

MIL-STD-1553 ϵͳʵʩ

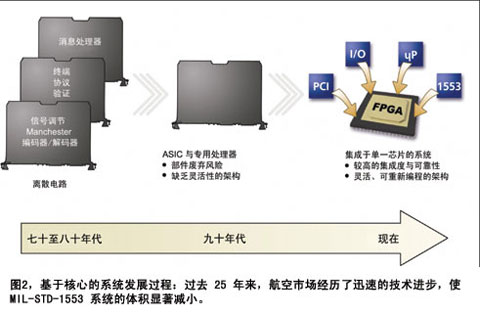

�������������缼��һ��,���յ����г��е� MIL-STD-1553 ���Ժͷ���ʵʩҲ�����˴��Ӵ�� DEC Unibus ���� 19 Ӣ���ͨ�����ܰ�װ�����,�ַ�չ������ VME �� PCI ϵͳ�ϵĽ�С����Ϊ���ɵĶ�ͨ������,�����ֳ����˸�С�����ɶȸ��ߵ� PCMCIA �ӿڡ�ͼ 2 ������ר�õ� MIL-STD-1553 ASIC оƬ�����̵�ʵʩ����ɢ��Э����շ���оƬ�龫��һ�����С�����ĵ͵� ASIC �ķ�չ���̡�

��ȥ,���͵� MIL-STD-1553 ϵͳһ�㶼�ɶ��COTS�������,MIL-STD-1553 I/Oͨ���ɵ�һ��Դ�Ĵ����ڲ��������ܵ� ASIC �ṩ,�����ڲ��������ṩ��Ϣ�����뻺���Լ��� MIL-STD-1553 ���������б����ȡ�ASIC �п��ܺ���Ҳ����û���� MIL-STD-1553 �����ṩ�����ӿڵ��շ��������ÿ�� ASIC Ϊһ��˫���� MIL-STD-1553 ͨ���ṩ�˹���,����֧�ֶ�� MIL-STD-1553 ͨ����ϵͳ����Ҫ��� ASIC ���շ�������ÿ�� MIL-STD-1553 ���ߵ�������ͨ�����ر�ѹ��ʵ�ֵġ��Ϻ�,��һ�����ɱ�̵� FPGA �豸�� MIL-STD-1553 ASIC ���ӵ���ϵͳ,���ṩ�����ϵͳ����,������ I/O���洢������ �ʹ������ӿڵȡ�

FPGA �ж����ܶ�,ͨ��������Ԫ�����������������ж�����ʽ�ܹ�,�ṩ�˷ḻ�� I/O ���ſɹ�ʹ�á�FPGA �����ṩ�ڲ�������������,��ǰ��Xilinx �Ƴ���һ���� FPGA ��������������ǰԼ������ 10 �������һ�������ڲ��ٶ�,�����˳ɱ���

�ִ� FPGA �����Ĵ�������ʹ���Ϊ MIL-STD-1553 ��ƽ������ѡ�������ΪԤ�ȶ���ġ��Ҿ������ԵĹ���,��Щ���ܿ���Ӧ�õ� FPGA ����С���ʹ����ʦ��Ϊ MIL-STD-1553 ʵʩѡ�� IP ��Ƶ�ԭ���кܶ�,���а�����

�������������������� IP ���Ŀ��������ؽ��ͷ����ķ��ա����ʦ����������ijһ���ض��IJ����������� FPGA �����̡�������ʱ���ܻᱻ�����ĵ�һ��Դ��ר�� MIL-STD-1553 Э�� ASIC�ʹ��������������췽�����γ��������ĶԱȡ��Ե�·ʵʩ FPGA��,��ƿ���ֲ�����µ� FPGA ��,һ�㶼����ı��书��,�����˶��������ģ�ͨ������Ŀ�гɱ��ϴ�IJ��֣���

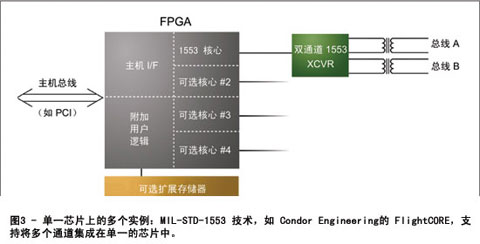

��С�� ������߿ɿ��ԡ������ĺ��������������ֹ���,������������I/O��MIL-STD-1553 �ͱ����·�ۺϵ���һ�� IC ��,�������ؼ��ٲ����������忨�ռ���ȸ��ɡ������������˿ɿ���,��������� MTBF�����ٲ����������Խ��ͷ����豸ϵͳ���������ռ估���ĵ�������ͼ 3 ��ʾ,�����Ա���Խ����ֹ����ۺϵ���һ�����豸��,�����˲����������������

���ͳɱ���������ʵʩ�� FPGA ����,�������������ڵijɱ�������ʱ����½���FPGA �۸�������������Ŀ�Ľ��ж��������»�,�� ASIC �ڳ��ڵ����������м۸�ȴ�����ǡ��ܶຽ�յ���ϵͳ�Ѿ���������в����� FPGA,һ�� MIL-STD-1553 ����ʵ���������ɵ��������е�оƬ��ͬϵ�е��������ܼ���оƬ�С���һ FPGA �м����˶�ͨ��ʵ���ɽ�һ����ʡ�ɱ�,ֻ��Ϊ��һ FPGA �ڿ������ɶ��ͨ���ӿڡ�

�������±�������� ��֧�ֶ��ֳ�Ӳ�������±��,���ĵ�ʵʩ������������Ʒ��ա����ϵͳ�������仯,����Ҫ��һ������ʱ,���� FPGA ����ƿ����������Ŀ����½�����������������Ի�������Ӳ��������ɺ�,��Ӳ�����������������ֹ��ܡ�����,����ڼ��ɽη�������������Ч����Ӧһ��ʵ ʱ�¼�,���Խ��ù������Ƶ� FPGA ����,�����ͽ�ԭ������ʵ�ֵĹ���ת��ΪӲ�����ܡ�

��Ӧ���ֻ��������������±�̵Ľ����������Ϊ���ֻ��幹�ܻ���Զ���;������Ƶķɺ��������Ͽɸ����� (LRU)������ USAF�� NATO �Ķ��ֻ�����ô� MIL-STD-1553B �����������Э��,���Զ��ֻ���� LRU ��Ҫ���ɱ�̵���ơ�ijЩ���ʵʩ��ͨ��������ӵ�ַ��ģʽ����Э�����Ѱַ��չ�����ݼ����ܶ�̶����Ϳ���ת���ɻ�ͬʱ�����˽��ϵ� MIL-STD-1553A �� MIL-STD-1553B LRU,���Ҫ�����߿����������������ܹ�������ͬ��Э�顣

��MIL-STD-1553 ϵͳ��Ʋ��û��ں��ĵ�ʵʩ

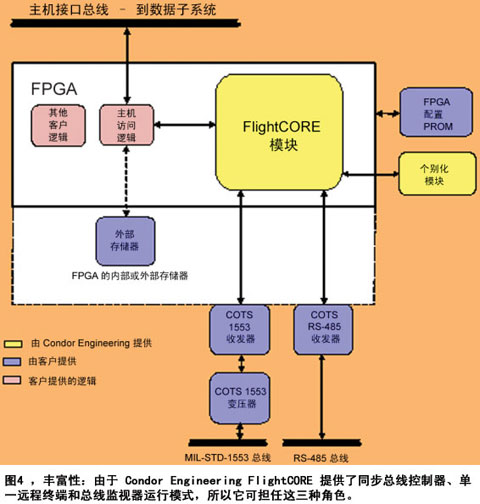

�ִ� FPGA ��ǿ����ʹ���Ϊ MIL-STD-1553 ��Ƶ�����ѡ��,����� Condor Engineering �Ƴ� FlightCORE ��ԭ��FlightCORE ��һ�����������Ա�ڸ��� Altera �� Xilinx �� FPGA������ʵ���ް�Ȩ��ʵ������Ƶ� MIL-STD-1553 IP�����������,����Xilinx �ۺϼ��� (XST) �� Altera Quartus II �����ۺϼ��� (QIS),FlightCORE 1553 �����������ڳɹ��ؼ��ɡ���ͼ 4 ��ʾ,�û�ֻ�뽫 Condor Engineering �� IP ���������������� Condor Engineering �ĸ���ģ�� (3mm x 3mm) ����,����ʵ�ָ����ܵ� MIL-STD-1553��ơ�FlightCORE ������������Աѡ��洢���Ĵ�С��ǡ�õ�����ϵͳ������ƥ�䡣ͼ4����ʾ�˿���ʵʩ�ڲ�������/���ⲿ˫�˿�������������ò�Ʒ���ṩ�� Manchester II��������롢��ϢЭ����֤��Ϸ�����Ϊ�ӿڿ��ƺͱ��ʵʩ�Ĺ��������ܹ������еı�Ҫ�����ֻ�������ⲿ�շ�������,�����COTS MIL-STD-1553��RS-485�շ�����

��һоƬ�ϼ��ж��ʵ��

&nb

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/12/02 16:57������FPGAֱ��������Ƶϵͳ�����

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

- ...2011/11/07 15:10������FPGA��ͨ���첽�շ������

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�����ݲɼ�ϵͳ���

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������