ʵ�ֲ�ִ�������ķ���

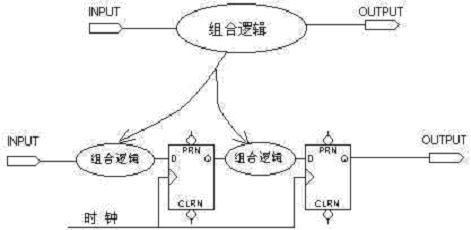

ͼ1�Ǻܶ�Ϊ�����ϵͳʱ�Ӳ��õIJ�ִ�������ķ���������û���ṩ������β�ֵ�ʵ�����Ҿ���ʵ��������Ҫ�ġ����Ҳ�������д����ʱ�����֪������д�ᱻ�ۺϳ�һ���ܴ������һЩ�Ŀ����뵽(�����ļ�����Ӧ�÷ֳɶ������)�����Ǹ����ӵ�ʵ���Dz������⡣

ͼ1

����ͨ����ˮ�ߵķ�ʽ�ֲ����������Ҳ��һ�����оƬ�ٶȵ�һ�ַ�ʽ�� ��������м����Ĵ�������Ƴ���ˮ�� �ܵ��͵����Ӿ��ǵ������������64�������������м����ʱ̫������������ϵͳ�ٶ�Ҫ����ʱ��Ϳ�������һ��16���ȣ�һ��4���ȣ������64���ȵĹ��ܡ�

�üӷ��������ӣ�������ABCD���OUT �ϰ벿�־��ǣ� out = A+B+C+D;

�°벿�־��ǣ�

always @(posedge clk)

begin

sumreg1 <= sum1;

sumreg2 <= sum2;

sumreg3 < = sum3; end

assign sum1 = A+B;

assign sum2 = C+D;

assign sum3 = sumrge1+sumreg2;

assign OUT = sumreg3;

ͨ������ʹ���°벿�ֵ��㷨���������ʹ����ˮ�ߡ�

ͨ���������ģ�û�����ӿ������Dz������⣬����һ�о�������Ӿͷdz�����ˡ���Ҳ��ѧ�Ÿ��������������Ӽ���255,�����һ���Ĵ���������ô��Ҫ�������Ϊ8��,������Ϊ������ôֻ������Ϊ4�������Ĵ���,���������С,��֪���Բ��ԡ�

reg[3:0]ad1;

reg[3:0]ad2;

always @(posedge clk)

if(!rest)

begin

out<=0;

ad1<=0;

ad2<=0;

end

else

if(ad1==15)

begin

ad2<=ad2+1;

ad1<=0;

end

else

if (ad2==15)

begin out<=1;

end

else

ad1<=ad1+1;

ad1������ȥ����ad2�ӡ�

always @(posedge clk)

if (reset)

counter0 = 0;

else

counter0 = counter0 + 1;

always @(posedge clk)

begin

counterreg0 <= counter0;

if (counterreg0 == 4'b1111)

outreg0 <= 1;

else

outreg0 <= 0;

end

assign counter1 = counterreg1 + outreg0;

always @(posedge clk)

begin

counterreg1 <= counter1;

if (counterreg1 == 4'b1111)

out <= 1;

else

out <= 0;

end

lflhust д�ij���û�дﵽ����ֵ�Ŀ�ģ� ԭ��ܼ� �Ǹ������ۺϺ����ɵĵ�·����ˮ����Ȼ���1�� zf0579�Ǹ��������ˮ����Ȳ���2���ﵽ�˲�ֵ�Ŀ�ġ� �����ij����㲻��дHDL���룬������д����ǰ��������Ҫ�� ����Ҫʵ�ֵ����ĵ�·�ṹ��

�����ij����㲻��дHDL���룬������д����ǰ��������Ҫ�С�����Ҫʵ�ֵ����ĵ�·�ṹ��

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������