C64x+ �� C64 �ں˵���������

��������(TI)������Ӧ�ù���ʦ ������

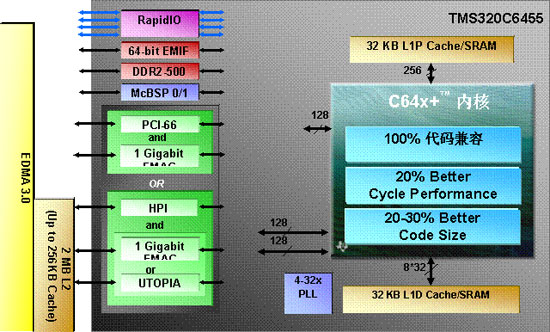

���ԣ�Ŀǰ�����е�TI������DSP��TM320C6455(���ļ��ΪC6455)��SoC��TMS320DM6443/6(���ļ��ΪDM6443/6)������C64+���ںˣ�C64x+�ں�һ��������C64�ں����ƣ���һ����ӽṹ�ϼ����������˸Ľ�������ߴ���������������Ҫ���ں˽ṹ��ָ���Ͻ���C64+�ں������C64�ں˵���������������ҵ�ڹ���ʦ�ڻ���C64+���ں�Ӧ�ÿ��������У��ܹ�������������ܡ�

�ؼ��ʣ�C64��C64+��SPLOOP������ָ��

TI���Ƴ���C64x+�ں���ȫ����C64x���������ڻ���C64x�ij�����C64x+��ֲ���ṹ��ͬ����64��ͨ�üĴ�����֧��32bit��40bit��64bit���������ͣ�Ҳ֧��8bit��16bit����������ͣ�����A0-A2��B0-B2�����������Ĵ���������һ��Ĺ��ܵ�Ԫ(A��B��)���Է��ʵ�����һ��(B��A��)��ͨ�üĴ����еIJ�������ָ���ϼ���C64x�ں˵�����ָ�����������������������������

1. ����49��ָ��

�Գ˷����ܵ�Ԫ(M unit)Ϊ�����õ�Ԫ�ĵĸĽ�������ָ��Ӵ��˳˷����������֧��32bit�˷��������˷���ʹÿ����16��16��MAC����8����������������ʾ��

����C64x��C64x+���������������˷�((dre+dim*i)*(cre+cim*i)=pre+pim*i)�����ֱ����£�

����C64xʹ����������ָ��ʵ�֣�

DOTP2 dre_dim, cim_cre, pim ;dre_dim��cim_cre�ֱ��ǽ�����������ʵ;�鲿����16bit���з�������������Ľ��

;���һ��32bit����������һ��ͨ�üĴ����С� DOTPN2 dre_dim, cre_cim, pre

������C64x+ֻ������һ��ָ��Ϳ���ʵ�֣�

CMPY dre_dim, cre_cim, pre:pim ; pre:pim��һ���Ĵ����ԣ��ֱ��Ÿ����˷�;�����ʵ�����鲿��

ͼ1

�����������Σ������ˮ���źã����Կ���C64x+ ��C64x���Լ��ٴ�Լһ�����ҵĸ����˷���������ͬʱҲ�����һ��ָ����ռ�õij���ռ䡣����������ADDSUB��ADDSUB2���µ����ݴ�����ָ����DPACKX2��Ҳ�������DSP�ڴ���DCT��FFT�任��������ܣ�����ָ��������DSP�Ĵ������ܷ���Ͳ�����ϸ���ܡ����ʹ����Щ��ָ��Դ���256���FFT�仯Ϊ��������ָ��仯��ͼ1��ʾ��C64x+��Ҫ803��ִ�����ڣ���C64x��Ҫ1246��ִ�����ڣ�C64x+�ij����СΪ664 bytes��C64x��СΪ1000 bytes���ɴ˿ɼ�C64x+�ؽ��������TI��DSP����ý�巽��Ĵ���������

2. ����������ˮ����(SPLOOP Buffer)

C64x�ܹ��г������������ˮ(Software Pipeline)��һ������DSP�Ĵ������ܣ���һ������Կ˷�������ָ�����ʱ����ɵĶ�CPU�������ܵ�Ӱ�죻��һ���滹��������ˮ�����н�ÿ���������һ���������������C64x+���������������ŵ㣬�����иĽ�������SPLOOP (Software Pipelined Loop)����Ӳ���ϻ���������ˮ����(SPLOOP Buffer)�������֧�֡�SPLOOP�������C64x+�ں��е�SPLOOP Buffer����������ˮ�е�ѭ����(Loop Kernel)�������У������¼������ƣ�

- ��������Ĵ��룬����prolog��epilog����β���Ҫֱ�Ӵ����ʶ�����Կ��Լ��ٴ���ijߴ磻

- ��ͬ��C64x��������ˮ�������жϣ�

- ����ѭ�����Ѿ�������SPLOOP Buffer��һ������Լ��ٶ�L1P Cache�ķ���Ƶ���̶ȣ��ɴ˽�ʡCPU��L1P Cache�Ĵ�������һ����Ҳ���Խ���CPU�Ĺ��ģ�

- ÿ��ѭ���ں˵�ִ�н�����ת���´�ִ�п�ʼ��ʱ�Ǿ�����ת���ɴ˲���Ҫ��תָ���֧�֣�

SPLOOP Buffer�϶���Է� 14��ִ�а� (execute packets)���ڳ����������У�CCS���Զ������Է���CPU��SPLOOP Buffer��ָ��������ָ����棬��˶���C/C++������˵��ʹ�úܷ��㡣

3. ֧�ֽ���ָ��(Compact Instructions)

C64x DSPֻ֧�ֱ���ȡָ��(��ͼ2A��ʾ)����C64x+֧�ִ���ͷ����ȡָ��(��ͼ2B��ʾ)��ָ���ͷ��ע�˸�ָ���������7�����У���Щ��32 bit�IJ����룬��Щ��16 bit�IJ����롣֧�ֽ���ָ��һ������Խ�ʡ����洢�ռ䣻��һ����Ҳ��˿������ӳ���Cache�������ʡ���ͼ3���γ���ʵ����ͬ�IJ���������9��ָ�����ڣ�ͼA����C64�ں˵Ĵ洢�������Ҫ48 bytes��ͼB����C64x+�ں˵Ĵ洢���ֻ��Ҫ32 bytes��

ͼ2

ͼ3

4. ֧����Ȩϵͳ

���ǵ�ĿǰԽ��Խ��Ŀͻ���TI��C6000ϵ��DSP�����в���ϵͳ��ͬʱԽ��Խ���C6000ϵ��DSP�����ն��豸��(IP STB��ʹ��DM642/3��DM6446/3)��Ϊ֧�ִ���ϵͳ�쳣����洢�ռ�Ƿ����ʵ�³���ԣ�C64+��ʼ֧����Ȩϵͳ��

��Ȩϵͳ������ģʽ��Ϊ��ȫ�����û�ִ��ģʽ������ϵͳģʽ������ȫ�����û�ִ��ģʽ�£� ���������ȫ�������еĿ��ƼĴ������������з���Ȩ�ij�������ϵͳģʽ��Ϊ�����û�ִ��ģʽ����ͨ�û�ģʽ������ϵͳ�����ڳ����û�ִ��ģʽ��ϵͳ�����ε�API��������ͨ�û�ģʽ�¡�

ͼ4

����������������ɼ���C64+�ں˵�������������һ����Ӧ������ԣ�һ�����ǿ����ý�巽��Ĵ�����������һ���������Բ���ϵͳ��֧�ֵ�³���ԡ�ͬʱҲͨ��֧�ֽ���ָ��洢��ȡָ�ķ�ʽ������ϵͳ���̱�������Ĵ���ߴ硣ͼ4Ϊʹ��C64+�ں˵�TMS320C6455�Ľṹ�����Կ�����DSP��Ƭ�ϴ洢�ռ��C6416�ֱ����һ��֮��(L2 Memory�ﵽ2MB��L1P��L1D��Ϊ32KB)�����ں���ִ�����ܺʹ����С�Ϸֱ��C64�ں����20%��20%-30%������TI��C64+�ں���ҵ�ڹ���ʦ���ܵ�TI��������DSP�������ܷ���ij�ŵ��

����Ķ�:

- ...2011/09/05 16:43������DSP TMS320C6416�������±�Ƶ����

- ...2011/08/31 15:12������XC2C64AоƬ������¼���ʳ��źż���·���[ͼ]

- ...2011/05/20 10:40��TI C64x+ DSP CACHE һ���Է�����ά��

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������