����AD7892SQ��CPLD�����ݲɼ�ϵͳ�����[ͼ]

��ϵͳ��AD7892SQ��CPLD(���ӿɱ��������)Ϊ���������һ����·�źŲɼ���·������ģ���·���á����ɷŴ�A/Dת����CPLD���Ƶȡ�����Ӳ����������Verilog HDL��̣�ͨ������CPLDʹ���ݲɼ���ʵʱ�Եõ���ߡ�

1 Ӳ�����

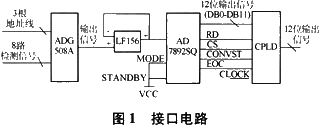

��Զ�·�źŵIJɼ�����ϵͳ����4/8ͨ��ADG508Aģ���·�������Լ����źŽ���ѡ��CMOS���ٷŴ���LF156��ѡ�е��źŽ��зŴ�AD7892SQʵ���źŵ�A/Dת����CPLD��ɿ��ƹ��ܡ���·��ͼ1��ʾ��

AD7892SQ������AD��˾������LC2MOS�͵���Դ12λA/Dת�������ɲ��л��������

AD7892SQ A/Dת�������������ص㣺����Դ����(+5V��+10V)���ڲ����в������ַŴ��������и��ٵĴ��кͲ��нӿڡ�

AD7892SQ�����ֵĹ������£�

a)MODE����������֣��͵�ƽʱΪ����������ߵ�ƽʱΪ�����������ϵͳΪ���������

b)STANDBY����������֣��͵�ƽʱΪ˯��״̬(����5mW)���ߵ�ƽʱ����������һ��Ӧ��ʱ�Ӹߵ�ƽ��

c)CONVST������ת������ˣ����˽��ɵͱ��ʱ��ʹ�������������ֿ�ʼת����Ӧ��һ������25ns�ĸ�����������ת����

d)EOC��ת�������źţ�ת������ʱ���˽����100ns�ĵ͵�ƽ���壻

e)CS��Ƭѡ���͵�ƽ��Ч��

f)RD���͵�ƽ��Ч����CS��϶���ʹ���������

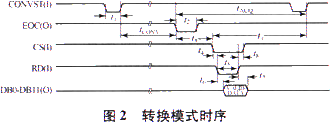

MODE�ŽӸߵ�ƽʱ��AD7892SQΪ���������ʱ����ͼ2��ʾ��

��EOC�½���ʱ���ڿ�ʼ����������ת��һ�����Ϳ�ʼ�´β���������ʱ��fACQӦ���ڵ���200ns��400ns��ת��������(��E0C���½���)����CS��RD��Чʱ������t6=40ns��ʱ�䣬�Ϳ�����DB0-DB11�ϻ��ת��֮���12λ���ݣ�CS��һ���Ƭѡ�ź���ͬ������һֱ��Ч�����RD��ʱ��T5ҲӦ����35ns��CONVST�ź�t1Ӧ����35ns����������ʱ�������������ڱ���״̬����ʼA/Dת����ת�������ʱ��tCONVΪ1.47μs��1.6μs��ת��������EOC�������t2Ϊ���ڵ���60ns�ĸ��������������жϻ��������档�ɴ˵ó��´β����ͱ��ε��������ͬʱ���У���˽�С��һ�β���ת�������ʱ��Ϊ1.47+0.2=1.67μs(600kSPS(ǧ�β���ÿ��))���ϴ�1.6+0.4=2μs(��500kSPS)��ͼ2�е�t9���ڵ���200ns��t7����Ϊ5ns��t3��t4��t8��Ϊ0��(��ʱt9=tACQ)��

2 �������

2.1 ϵͳ����

ϵͳ�е�CPLD�ǽṹ�Ƚϸ��ӵĿɱ����������Ӳ������������ƵĿ��Ƴ���д��CPLD�ڼ���ʵ���书�ܡ�ϵͳ�ɼ������ݳ����������ݻ������У����ݻ�����Ҫ���Ҫ����A/Dת��оƬ�Ľӿڣ���Ҫ����ϵͳDSP�Ľӿڣ���������������ʣ���ϵͳѡ��FIF0(�Ƚ��ȳ�)������FIF0���в���Ҫ��ַѰַ���ŵ㡣

2.2 ϵͳ����������

��ϵͳ����Verilog HDL���Խ���������VerilogHDL����90%�İ뵼�幫˾ʹ�ã���Ϊһ��ǿ�����ƹ��ߡ����ŵ��ǣ�

a)Verilog HDL��һ��ͨ�õ�Ӳ���������ԣ���ѧ���ã�

b)Verilog HDL������ͬһ����·ģ���ڽ��в�ͬ�����ε�����������߿��Դӿ��ء��š�RTL������Ϊ�ȸ�����ζԵ�·ģ�ͽ��ж��壻

c)����������е��ۺϹ��߶�֧��VerilogHDL������Verilog HDL��Ϊ����ߵ���ѡ���Ե���Ҫԭ��֮һ��

d)���е����쳧�̶��ṩ����Verilog HDL�ۺ�֮����������Ԫ���⣬���ʹ��Verilog HDL������ƣ������ڸ��㷺�ķ�Χ��ѡ��ί������ij��̣�

e)PLI(������Խӿ�)��Verilog HDL���Խ���Ҫ������֮һ����ʹ������߿���ͨ���Լ���дC����������Verilog HDL�ڲ������ݽṹ��

2.3 AD7892SQ����

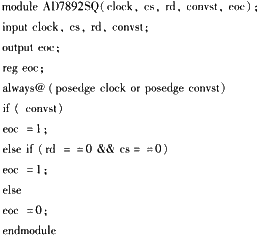

����AD7892SQģ�飬����ģ�����ڲɼ�ϵͳ�ķ��棬����֤FSM(����״̬��)��Ƶ���ȷ�ԡ���ģ����Ҫ��4�������źź�1������źţ���оƬ�Ŀ����ź�һ�¡��������£�

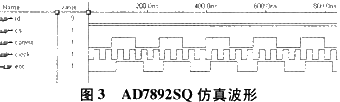

AD7892SQ���沨�μ�ͼ3��

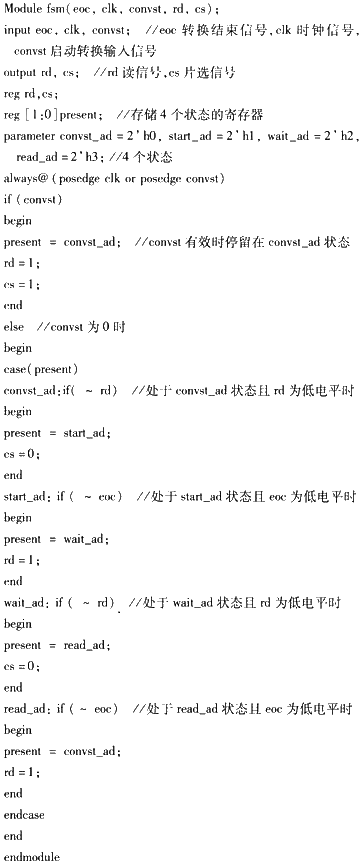

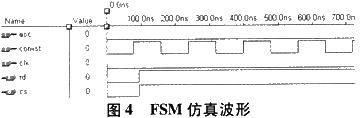

2.4 FSM����

FSMΪ�첽��������convst��Чʱͣ����convst_ad״̬����rd��cs��Ϊ1��convstΪ0�Ҵ���clock��������ʱFSM�ᴦ��4��״̬�е�һ��״̬��ͼ4ΪFSM���沨�Ρ�

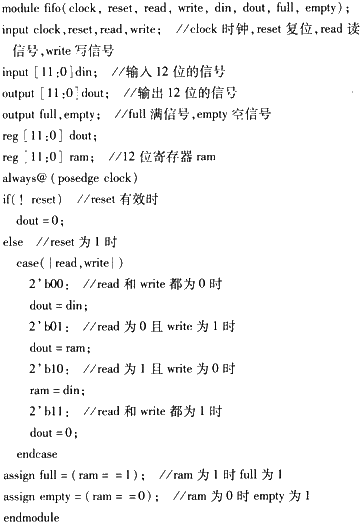

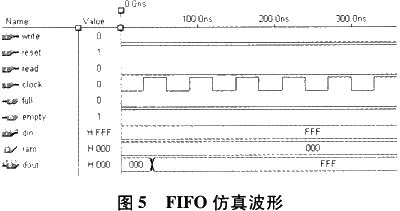

2.5 FIFO����

FIFOΪͬ����������reset��Ч�Ҵ���clock��������ʱ��doutΪO��resetΪ1�Ҵ���clock������ʱ��read��write��ϵ�4������ֱ��Ӧ���ԵĹ���״̬��ͼ5ΪFIFO���沨�Ρ�

3 ������

Verilog HDLӲ������������Խ��Խ�㷺��Ӧ����EDA(��������Զ���)������EDA��ƹ���ʦ����������ASIC(ר�ü��ɵ�·)��ƺ�CPLD/FPCA�������ø����Խ��е�·��ƣ��ܹ������IJ��������Ҽ��������˵�·��Ƶ�ͨ���ԺͿ���ֲ�ԡ��Ϻ���Ҫָ�����ǣ�����IP�˵ķ�����Ƶ�·���������Ե���ʹ�ã����ҿ���Ƕ�뵽ASIC��CPLD/FPGA�ĵ�·����У�ͬʱ�����˲�Ʒ�Ŀ������ڣ�Ӧ�����ƹ㡣

���ߣ������� ����� ����ݼ ��Դ�����ӹ���ʦ

����Ķ�:

- ...2013/10/16 13:40������AXIe �� PCIe �ߴ�������ģ��ͬ�����ݴ���ĸ���ͼ�δ���ϵͳ

- ...2012/04/23 12:15������AVR��Ƭ������Ƶ��Դ����ϵͳ

- ...2012/03/31 14:49��ʵ�ֻ���ARM��Ƕ��ʽϵͳ��SoC����

- ...2012/03/22 11:18�����ڣ��Σƣɣӵĺ��ײɿ����߿���

- ...2012/03/20 14:53�����ڣ��ģӪ��µķɻ�Ԥ����ײ�㷨�о�

- ...2012/03/14 14:36������ARM�������ĵ�Ŀ�Ӿ���ඨλϵͳ

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...�� ���ݲɼ��ն�ϵͳ�豸

- ...�� ���ǿƼ�̤��������

- ...�� ����˼® ���� AEC-Q100 ������֤������ϵ�в�Ʒ�ƻ�

- ...�� ����˼® ������������� �ѽ�ϵ��™ FPGA ��Ʒ �ѽ�ϵ�в�Ʒ���������� 1M ����Ԫ�� FPGA

- ...�� ����˼® ����Trion® Titanium ��̨���� (TSMC) 16�����սڵ���Ƭ

- ...�� TI��2019��ȫ����ѧ��������ƾ����佱�����ھ�����

- ...�� BlackBerry QNX��������ȫ����������ȫ�����Եȼ�(ASIL) ��D����֤

- ...�� ��������ѡ��BlackBerry������һ������