ʱ��ʱ�Ӷ���������һ��

���ߣ�Thomas Neu

�������� (TI) ϵͳ��Ӧ�ù���ʦ

���͵ĸ��� ADC ���߱���ģ�����������ԼΪ�ϴ����Ƶ�ʵ� 3 �� 6 ������������ǿ�����������Ƿ����Ӧ���С�ADC ��ƵĽ��½�չ�������չ�˿������뷶Χ������ϵͳ�����Ա�����ȥ������һ���м�Ƶ�ʼ����Ӷ����ͳɱ����ġ���Ƿ�������ջ�����б���Ҫ�ر�ע�����ʱ�ӣ���Ϊ��һЩ������Ƶ����ʱ�Ӷ������Ϊ��������� (SNR) ����Ҫԭ��

��ϵ�����¹��������֣����� 1 ���֡��ص�������ȷ�ع���ij��ʱ��Դ�Ķ������Լ���ν����� ADC �Ŀ�������ϡ��ڡ��� 2 ���֡��У�����϶��������ڼ��� ADC �� SRN��Ȼ������ʵ�ʲ�������Աȡ����� 3 ���֡����������ͨ������ ADC �Ŀ���������һ������ ADC �� SNR�������ص����ʱ���ź�ת�����ʵ��Ż���

���������ع�

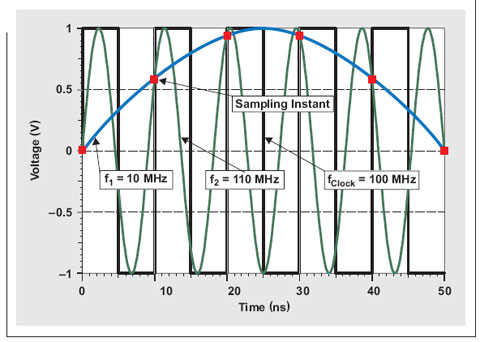

���� Nyquist-Shannon ���������������������������ϴ�Ƶ�ʵ���������ԭʼ�����źŲ�����������Եõ���ȫ�ؽ��������� 100 MSPS �����ʶԸߴ� 10MHz �������źŲ������ܸ��ź���λ�� 1 �� 10MHz �Ļ�������Nyquist ���������� 100 �� 110MHz �ĸ��� Nyquist ������Ƿ��������û��ϵ����μ�ͼ 1�����ڸ��ߣ��ڶ������������ȣ�Nyquist �����в�����һ�㱻����Ƿ������β�����Ȼ������ ADC ǰ��Ҫ��ʹ�ÿ�������ˣ��Զ����� Nyquist ���������ͬʱ�����ؽ�ԭʼ�źŹ����в������š�

ͼ 1 100MSPS ���������������ź���ʾ�˻����������ͬ������

��ϸ�۲�ij�������㣬���Կ�����ʱ����ʱ�Ӷ�����ʱ����λ������������γ�����仯�ġ����ڸ� Nyquist �������磬f1 = 10 MHz �� f2 = 110 MHz��Ƿ������������Ƶ�ʵ����ӣ��̶�������ʱ�Ӷ������������������������������ƫ������������⣬ͼ 2 ����ʱ���ź�����ת�����ʶԲ���ʱ��ı仯������Ӱ�졣ת�����ʾ�����ʱ���ź�ͨ���㽻���Ŀ��������仰˵��ת������ֱ��Ӱ�� ADC ��ʱ�ӵ�·�Ĵ�����ֵ��

ͼ 2 ʱ�Ӷ����γɸ�����������ź�������

ʱ�Ӷ������µ� SNR ����

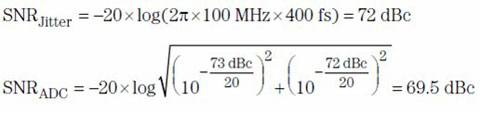

�м������ػ����� ADC �� SNR�����磺��������������ʽת������һ�㲻���ԣ��������������ڵ�����Ƶ�������� SNR�����Լ�ʱ�Ӷ�����SNRJitter������μ����淽��ʽ 1����SNRJitter �����ܵ�����Ƶ�� fIN��ȡ���� Nyquist �������ƣ�ͬʱ����ʱ�Ӷ����� tJitter �����ƣ�����㷽�����£�

SNRJitter[dBc]=-20��log(2����fIN��tJitter)(2)

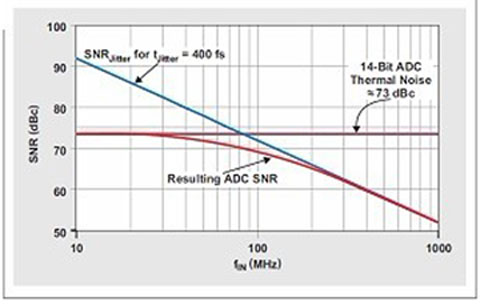

��������Ԥ�Ƶ����������ù̶�������ʱ�Ӷ�����SNR ������Ƶ���������½���ͼ 4 ������������������ʾ�� 400 fs �̶�ʱ�Ӷ���ʱһ�� 14 λ����ʽת������ SNR���������Ƶ������ʮ�������磺�� 10MHz ���ӵ� 100MHz����ʱ�Ӷ��������Ľϴ�ʵ�� SNR ���� 20dB��

��ǰ���������� ADC SNR ����һ����Ҫ������ ADC �����������䲻������Ƶ�ʱ仯��һ�� 14 λ����ʽת����һ���� ~70 �� 74 dB ������������ͼ 4 ��ʾ�����ǿ����ڲ�Ʒ˵�������ҵ� ADC �������������൱�ڽϵ�ָ������Ƶ�ʣ�������Ϊ 10MHz���� SNR������ʱ�Ӷ���������һ�����ء�

����������һ������ 400 fs ����ʱ�ӵ�·�� ~73 dB �������� 14 λ ADC ���з�����������Ƶ�ʣ����磺10MHz �ȣ��£��� ADC �� SNR ��Ҫ�������������塣��������Ƶ��������400-fs ʱ�Ӷ���Խ��Խռ��������ֱ�� ~300 MHz ʱ��ȫ�ӹܡ�������� 10MHz �� SNR��100MHz ����Ƶ����ʱ�Ӷ��������� SNR ÿʮ��Ƶ���� 20dB�������� SNR ������ ~3.5 dB������ 69.5dB������Ϊ���� 73-dB ����������μ�ͼ 5����

���ڣ������ԣ���� ADC �����������ӣ��Ը�����Ƶ�ʲ���ʱʱ�Ӷ�����dz���Ҫ�����磬һ�� 16 λ ADC ���� ~77 �� 80 dB ���������㡣����ͼ 4 ��ʾ����ͼ��Ϊ�˽�С�� 100MHz ����Ƶ�� SNR ��ʱ�Ӷ���Ӱ�죬ʱ�Ӷ�����Ϊ��Լ 150 fs ����ߡ�

ȷ������ʱ�Ӷ���

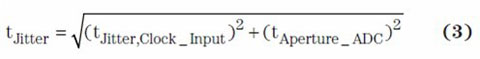

��ǰ����������ʱ�Ӷ�����ʱ�ӵļ�ʱ������λ�������� ADC �Ĵ��ڶ�����ɡ����������ֽ��������£�

�����ڲ�Ʒ˵�����п����ҵ� ADC �Ŀ��ڶ��� (aperture jitter)����һֵһ����ʱ�������ת������һ��ָ������ס��һ�����Ҫ����ʱ�����������ת�����ʣ��Ӷ����Ӵ��ڶ�����

ʱ�����붶��

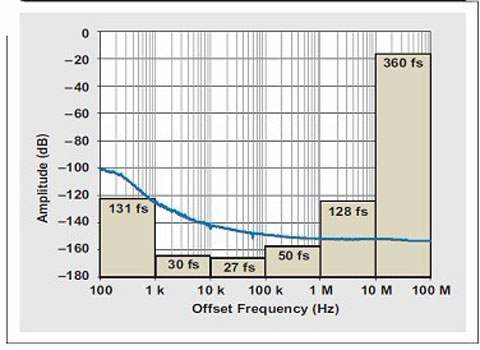

ʱ������������ʱ�ӻ������� PLL�����������������һ��涨��ij��Ƶ�ʷ�Χ�ڣ���Ƶ��ͨ��ƫ���ڻ���ʱ��Ƶ�� 10 kHz �� 20 MHz����λҲ������������Ƴ���λ����ͼ�������Խ������ϵ�һ���ȡ������Ϣ�����ǣ��Ͷ˵� 10kHz �߶˵� 20MHz ��ʱ������ȷ��ʹ�ñ߽磬��Ϊ���ǵ�������������ϵͳ���������ǽ��ں��������ϸ���ܡ�ͼ 6 ������������ȷ�������Ƶ���Ҫ�ԣ�ͼ�е���λ����ͼ����ÿʮ��Ƶ�������ݸ��ǡ����ǿ��Կ���������������趨Ϊ 100-Hz �� 10kHz ƫ�ƣ�������Ķ����㼫Ϊ��ͬ��ͬ���أ����磬��������������Ϊ 10 �� 20MHz���ɵõ���� 100MHz ���ü�Ϊ��ͬ�Ľ����

ͼ 5 ������ ADC SNR ����������ʱ�Ӷ���������

ͼ 6 ÿʮ��Ƶ����õ���ʱ����λ��������Ӱ��

����Ķ�:

- ...2012/04/01 10:31��ʱ��ʱ�Ӷ���������һ��

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������