��ż��ݼ����ھ�̬�����е�Ӧ��

ժ Ҫ����̬�����ĵ�ż�����Ӱ����ɿ��Ե�һ����Ҫ���档���ݵ�ż��ݵĸ���Դ������;���������豸��Ҫ�أ������˾�̬�����е�ż��ݵĻ��������;���ʵ�ַ�����

�ؼ��ʣ���̬��������ż��ݼ���Ӧ�ã��ɿ��Ԫ�

1����

�ڼľ�̬������һ��ʹ�õ�����·��Ϊ�����ĸв������ʹ�ô�ͳ�ĵ��Ԫ����Ϊִ�л������ڸв�����ĵ�·�м���ģ���·�������ֵ�·���ڸ��ӵľ�̬�����ж��ձ�ز����˵�Ƭ��������ʹ����������������ܿ��ƴ���������һ̨�������ܾ������ִ�ͳ�����Ĺ��ܣ�ȡ����̨��ͳ�����������ۺϹ��ܵĵ�����ͬʱ�����������ܿ���������ͨ��Э�黹����ʵ�ֵ����ļ��п��ƺͼ�⡣������������ֲ���ͨ�������ںܸߵ�Ƶ���ϡ���Ϊ����Ԫ���������Ҫ���ֽ��ϣ��ڲ�Ԫ�����ľ���ܽ�����ˣ���������ͻ�е����ʽ����������ż�������ͱȽ�ͻ����

���Ƶ�Ÿ��ŵ������ǹ�ϵ��̬�����ɿ��Ե���Ҫ�о����ݡ�����ʵ�ʾ������һ̨���Ӳ�Ʒ�ĵ�ż����Ի�ֱ��Ӱ����ʹ�ü�ֵ������Ÿ������������ԣ����ij���û�����Եı�Ȼ�ԡ�������ȫ��֪��һ������������һ��Ԫ�����ڹ���ʱ�ܵ��ĸ�������Щ���Ƚ�ʵ�ʵ����������յ�Ÿ��ŵIJ�������Ԥ�Ȳ�ȡ��Ҫ�Ĵ�ʩ���ϴ��ȵؼ��ٵ�Ÿ��ŵ��γɡ���Ҫָ�����ǵ�Ÿ���������һ�����ӵ����⣬����������Ϳ��Էֳ�ʮ���֣����ǵ��γ�ԭ���Ԥ����ʩҲ���൱��ġ������漰����ֻ�����Ƶ�Ÿ��ŵIJ������ݡ�

2��̬������ż��ݵĴ�ʩ

�γɵ�Ÿ��ŵ������������������������ⷢ�͵�Ÿ��ŵ�Դ��������Դ���ڶ����д��ݵ�Ÿ��ŵ�;������������ϻ���䣻�����dz��ܵ�Ÿ���(����������)�Ŀ��塪�������豸�����ݲ�����Ÿ��ŵ����������Ƶ�Ÿ��ŵ�ԭ���Ӧ�Dz�ȡ�������������������Ե��������ʩ��������Դ���Բ����˲������ᡢ���Ρ�ȥ��ϵ�����������Դǿ�Ȼ������������ֶΣ����������ݵ�;�����Բ��ø��롢���Ρ��迹ƥ��ȴ�ʩ�������ŵ��豸���Բ����������ȡ�ʵ�е�Դ���ź��˲��Ĵ�ʩ��

��

2.1��������Դ������ǿ�ȵĴ�ʩ

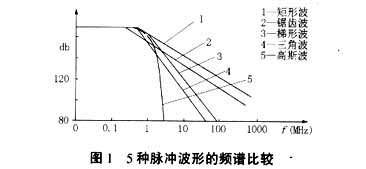

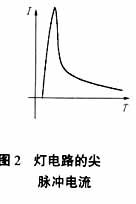

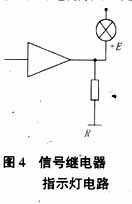

���ڴ����������ֵ�·�Ĵ��ڣ��ھ�̬�����ڲ�������Դʮ�ַḻ���������ź��У��Ծ��β��϶ࡣ�������ֵ�·ʱ������ָ��������Ƶ����Dz���ͼ1�Ǽ������岨�ε�Ƶ�ױȽϣ���ͼ1�п��Կ������β��ĸ�Ƶ���ַ������Ҫ�ߡ��������������������Ҫ���źŵĸ�Ƶ���ֲ��������ԶԲ������β��ĵ�·����Ӧ����ȡ���εķ�������ֹ������ķ��䡣�ı��źŵIJ���Ҳ���Ը��Ƶ�·�ĵ�ż����ԡ����磬�ڲ�Ӱ������ϵ�������£��ʵ����;���������������½�ʱ��ʹ֮�����β�����ʽ���֣�����Լ����źŸ�Ƶ���ֵķ��ȣ��Ӷ�ʹ����������١����źż̵�����ָʾ�Ƶ�·���ڼ�װ�˺��ʵ�Ԥ�ȵ���R�Ժ�����ָʾ�Ƶĵ������ξ���ͼ2����״��Ϊͼ3����״�ˡ�������������ͻ����ܵ����ơ���

2.2������������Ŀ���������

���ſ��Ծ��������������;���������������Ƿ�����������к��ĸ�����Ҫ�Ӹ��ŵ�ǿ�ȼ����������Ŀ���������(���������)��������������ŵ�ǿ�ȵ��������豸��������������Ӱ������������������ֻ�е����ŵ�ǿ���㹻����������������������ʱ����Ӱ��������������������ˣ���������Ŀ����������зdz���Ҫ�����á�

һ�������ֱ���������ޡ������������ޡ����������������������ֵ�·�ĵ�����������ޡ�

ͨ����������·��Ƭ���������״̬����������˵�״̬������������ֵ�·��Ƭ��������˵ĵ�ƽ�ܵ����ţ��Ϳ�������������״̬�����������������������ڵ�Ƭ��һ������˵�״̬�ǵ͵�ƽ����CPU��ȡ�˶�ʱ�Ͷ���һ����0����һ��͵�ƽ����һ��������ֵ�涨�ģ���ȷ������·����ĵ͵�ƽ����ڴ˹涨ֵ���������˵ĵ�ƽ�ܵ��˸���ʹ���ϵĵ�ƽ�����˹涨��������ֵ��CPU�Ϳ��������һ����1����������ֱ������������������CPU�жϵ�(��)��ƽ����ֵ����Χ����·ʩ����CPU������ϵ�ʵ�ʵ�ƽ֮�

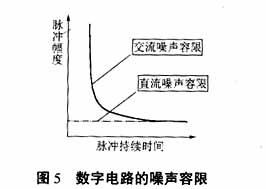

������ŵ�ƽ�ķ�����Ȼ�ܴ�����ʱ��ܶ���Ҳ�п��ܲ������������Ӱ�졣���磬һ�����ֵ�·��������ܵ��˸��Ų��ҵ�ƽҲ��������ֱ���������ޡ����ŵIJ���Ӱ���ǻ�����˵�·����ת���������ֵ�·�ķ�ת����Ҫһ��ʱ��ġ�������ų�����ʱ��̣ܶ��ڴ˶�ʱ���ڱ����ŵ����ֵ�·û�����ü���ת����ʵ���������û�й��ɶ����ֵ�·�ĸ��š�����������ŵ�·���ӳ�ʱ����һ���أ������ý���������������һ���������������Ŀ�����������һ��������ֱ����������Ҫ���佻���������ͣ����Ҹ��ŵ���������Ƶ��Խ�ߡ����ֵ�·�Ĵ���ʱ��Խ�������ֲ��Ҳ��Խ��ͼ5���Ե���������һ���ʡ�

��

���������������ŵ�·�ϵ�ʱ�������ŵ�·���迹�ܵͣ���������������һ���Ĺ��ʲ���������ŵ�·��ƽ�����Ա仯���������ŵ�·���迹Ҳ��Ӱ���·���������������ء�

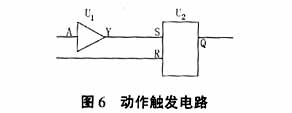

ͼ6��һ�������̵����Ĵ�����·��U1��һ����������U2�Ǵ�������U1�������Y����U2����λ��S��������·�ܵ�����ʱ��U2��Q���Ƿ���Ϊ���Ŷ���λ��Ҫȡ�����������أ�U1�������Y��ʵ�ʵ�ƽ��U��2�������S����ֵ��������U��2�ķ�תʱ�䣻U1��Ӧ�˵�����迹��U2��Ӧ�˵������迹��

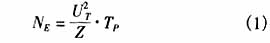

����ȿ��Ǹ��ŵĵ�ƽ���ֿ��Ǹ��ų�����ʱ�䣬�ٺ����ŵ�·���迹��ϵ��������ô�������������ͱȽ����������������ֵ�·�Ŀ��������ܣ�������������ͬʱ�����˸��ŵĵ�ƽ������ʱ������ŵ�·���迹������ͼ6�����ӣ�������(1)ʽ�������������������ޡ���

ʽ�У�NE���������������ޣ�

UT����������U2�����·��ֵ��

TP����������U2�Ĵ���ʱ�䣻

Z������·�迹��

(1)ʽ��Ȼ��������ͼ6������U1�����Y��U2��λ��S����һ��·��������������ƹ㵽һ������ֵ�·��

�������������������֪��������·���迹�����оƬ�ĵ�ƽ��ֵ���ӻ��䷭ת����ʱ�䶼������ߵ�·�������������ޡ�Ҳ��������˵�·�Ŀ�����������

���ڵ����̵�����˵���䶯��ʱ��һ��Ҫ���ں��뼶�������ֵ�·�Ĵ���ʱ�������뼶������ͼ6��ʾ�ĵ�·�У�U2ѡȡ����ʱ�䳤�ĵ�·����Ӱ�������̵�����ʱ���������·���迹��Ҫȡ����U1������迹������Ƶ�·ʱӦ����ѡ������迹�͵�оƬ�����⣬������������(ͼ��δ����)Ҳ��һ�ֽ�����·�迹�ķ�����

���п��ܽ��źŴ����ɵ�ѹ�����Ϊ�������䣬����������������Դ����ߡ�

��

2.3���ٸ�����������

�ھ�̬�̵����ڲ������ŵĴ���;���������ŵ��ߵĴ�����Ҳ�пռ�ķ��䡣����ڲ�û�е�Ƭ���������ʹ�źŹ����ڽϵ͵�Ƶ�����Լ��ٿռ�ķ��䡣�е�Ƭ��������£�����ʹ�õ�Ƭ���ڲ��Ĵ洢�����ܵ�Ԫ��������������һЩ���Ϻò�ʹ�ô���չоƬ�ĵ�Ƭ��ϵͳ�������ڲ��Ŀռ������п��ܽ��͡�ֻҪû�кܸ�Ƶ���źţ��Ͳ�������к��ķ�����ź���ϴ�����

����������Ȼ�����еĵ�ŷ�����ż����������ĸ��ţ���Ҫ�Ĵ�ʩ�Ǽ�ǿ���δ�ʩ�����ʩ�����ھ�̬������Ԫ�����ǰ�װ��ӡˢ��·���ϵģ����ӡˢ��·����������Ƶ�Ÿ��ŵ���Ҫ���ݡ���ʱ�ڿ�����ӡˢ��·�Ŀ����������Ҫ�������ԭ����·�����ܴﵽ�ϸߵ����Ƶ�Ÿ�����������·���ϵ�ӡ�Ƶ��ߺͽ��������ǹؼ����֡��ӵ�Ÿ��ŵĽǶ�˵��ӡ�Ƶ��ߵĺ�ȡ����ȡ����ȡ����衢��С�����ֵ���������������ڵ���Ĵ��ŵ����ؾ�����ӡˢ��·�ĵ�ż������������ڵ��������֡�ӡˢ��·��Ĺ�����ʽ��������ߵ�Ҳ�����ӡˢ��·ʱ���뿼�ǵ����ء�

��

3����

��̬�����ʹ�ͳ�ĵ��ʽ�̵�����ȴ��ڱȽ����صĵ�ż������⡣����������һ���Ե�Ÿ��Ž�Ϊ���еĵ����豸��Ҳ��һ�����ײ�����Ÿ��ŵ�����Դ���粻��ȡ�ʵ��Ĵ�ʩ����̬�����Ŀɿ��Ի����ڵ�ż���������ܵ�Ӱ�졣�ڵ�ż��ݵ������ϣ��ȽϿ��еĴ�ʩ��Ҫ�ǣ�

1)��������Դ������ǿ�ȣ������ź�Ƶ�ʡ��ı��źŲ�������֮��Ч�ķ�����

2)������������Ŀ�����������Ӧ��ȡһ������ߵ��������������Ĵ�ʩ��

��Ÿ���������һ�����ӵ����⣬���ǵ��γ�ԭ���Ԥ����ʩҲ���൱��ġ���������������ż������������ʱ��ȫ��������Dz����ܵġ��Ϻ�������ʹ�öԼ����Ʒ�ĵ�ż����Լ��ɿ�������Ҫ���塣��

�����

��1�����ɴ�����.���ӿ����豸�Ŀ����ż�����Ӧ�ãۣͣ�.��������е��ҵ�����磬1989.

��2��ɳ�.����һ�廯ϵͳ�ĵ�ż��ݼ����ۣͣ�.�������й����������磬1999.

��3��TI AC/ACT CMOS Logic Data Book�ۣڣ�.��

����Ķ�:

- ...2011/10/31 16:02������PCB�ĵ�ż��ݵ����

- ...2011/10/26 13:58��̽�ֵ�ż���EMC��Ƽ����Լ���

- ...2011/09/28 16:34��������ѧ�ڵ�ż��ݷ����е�Ӧ��

- ...2010/07/23 09:56����ż���֮��Դ�����豸

- ...2009/06/26 15:21��ANSYS�ں��պ�������ż��ݵ�Ÿ��ŷ����е�Ӧ��

- ...2009/06/26 14:32��ϵͳ����ż����Զ�����ϵͳ����

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������