TMS320C6678��������VLFFT��ʾ

����Ƥ��̽����TMS320C6678��������VLFFT��ʾ��ͨ������8���̶�����DSP�ں˵�TMS320C6678��������ִ��16K-1024K��һά�����ȸ���FFT�㷨�����������ֱ��ڲ���1,2,4��8��ʱ���Ե�����ʱ�䡣��ʾ�Ľ��֤����C66X DSP�ں˵��������ܣ��Լ�TMS320C6678����������ƽ�л�ִ���������ں����������ȵ����ԡ����ĵ���ʾ����FFT�㷨�����㷨������ҽѧ����ͨ�š����º���ҵ�״��Լ�����ս(����������������)�������б�Ƶ��Ӧ�á�������ʾ�����ʾ������������Ϊ1 GHz��DSP�ں�Ϊ8��ʱ����TMS320C6678������ִ��1024K��FFT�㷨����ֻ��Ҫ6.4���롣

TMS320C6678 SoC

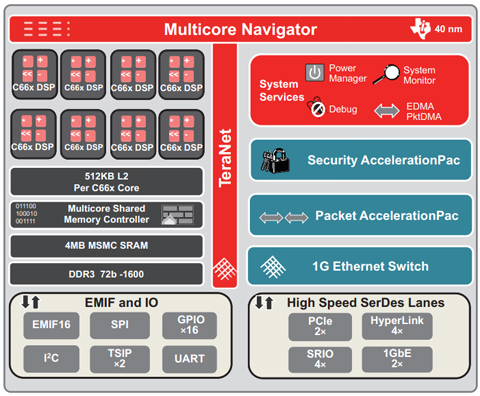

TMS320C6678����������8��DSP�ںˣ��ǻ���TI��C66x �̶�����DSP�ں��Լ� TI���ж��Ȩ���Ĵ�����KeyStone���ܴ����ġ��������ٶȽϸ߿ɴ�1.25GHz��������ٶ��������Խ���ÿ��160ǧ�״θ������㣬����ͨ����������ĵĵ��ܲ���10w��TMS320C6678����������ɫ����ÿһ��DSP�ں˶���512KB�� L2�ڴ棻���⣬8MB��оƬ�ڴ�����4MB�Ĺ����ڴ棬�����������ڴ涼�о����롣����DDR3������64λ�ģ���8λ�����룬�����ٶȿ��Ըߴ�ÿ��1600�ױ��أ�ͬʱ֧�ָߴ�8GB���ⲿ�洢�����ݴ�ȡ�����⣬TMS320C6678�������������PCle��Serial RapidIO® ��Gigabit Ethernet�Լ�TI��HyperLink���棬������������ӵ�TI������DSP��ARM�� ARM+DSP�������Լ���������FPGAʱ�����ṩ�ߴ�50Gbps�������ٶȡ�

�ڱ��ĵ�VLFFT��ʾ�У�TMS320C6678�����������ٶ�Ϊ1GHz��DDR3���洫���ٶ�Ϊ1333MHz��

ͼһ��TMS320C6678��ͼ

VLFFT��ʾ

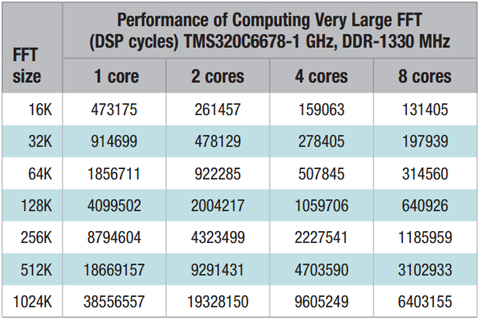

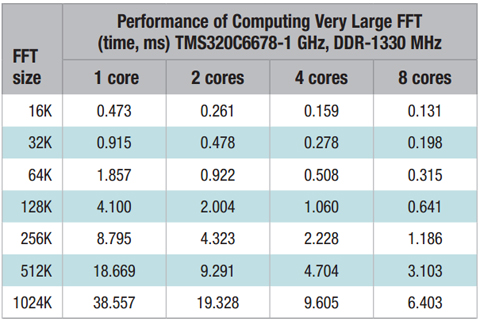

����VLFFT�㷨Ҫ����������ݴ���ڴ��������ⲿ�洢�����У��ڱ���ʾ�����У�����ͨ��DSP�ں˴�ȡ������ʹ������Ϻ��������ⲿ�洢���С�ͬʱ��������������ʼ�ձ���ѭ��������ʱ���������ʾʱ��ΪTMS320C6678���������ò�ͬ�������ںˣ�1,2,4��8���������㵱FFT��С��ͬʱ�Ľ������ЩFFT��������

��16K

��32K

��64K

��128K

��156K

��512K

��1024K

����ʾ�����У�ͨ�������㸺�طֲ�������˺���ȫ�������C66X DSP�ں˸����ܼ��������ķ�����ȷ��ִ��FFT�ﵽ�ϴ����ܡ�ͬʱ���û���ʱ���ȡ�㷨��һάVLFFT�㷨�����ƵĶ�άFFT�㷨��������ַ������������dz��������Nʱ���ֽ��N=N1*N2����ʽ���ڱ���ʾ�����У����һά��������dz��Ͳ���N1��*N2�еĶ�ά��������ʾ��Ȼ��ͨ�����²���������FFT��

1��

����N2��������N1�������в�ͬ��Сʱ��FFT��

2��

������ת���ӣ�

3��

�洢N2 ����N1�в�ͬ��СʱFFT�㷨�Ľ�����γ�һ��N2*N1�Ķ�ά���飻

4��

����N1��������N2�������в�ͬ��Сʱ��FFT��

5��

�洢�з����ϵ������γ�N2*N1��ά���顣

����㷨��Takahashi��ΪHitachi SR8000�ĸ�����ƽ��FFT�㷨��

��ִ�ж���㷨ʱ����һ���Ǽ���N2�У��˵���������N1�й���µ�FFT�㷨�����IJ��Ǽ���N1�У��˵���������N2�й���µ�FFT�㷨��0�������ˣ�����������ʣ�µĸ�����ͬ��������N1�����N2����Ĵ�С��ÿһ���ں˼��������FFT���������ֳɼ�����С��ģ������Ӧÿ����L2 SRAM�ڴ�Ŀռ䡣ÿһ�����ݶ�ͨ���ⲿ�洢���е�DMA Ԥȡ��L2 SRAM�ڴ��У�Ȼ��ͨ��DDR�����ݷ��ص��ⲿ�洢���С�ÿ���˶�����2��DMAͨ�����ⲿ�洢����DDR3�����ڲ��洢����L2 SRAM����ת���������������ݡ�

���

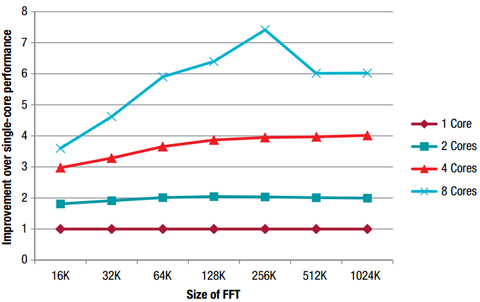

��ҳͼ��1չʾ��TMS320C6678������(TMDSEVM6678LE)�ֱ���һ��DSP���ں�һ�����뵥λʱ��������FFT����Ľ����������״̬�£������ڼ�����ں���������һ����ѭ�������ͻ����һ�롣������ʵ�У����ڴ�����Ϣ���е��컨�壬ͬʱ�������ڴ��С����Ϣ���ȣ��ڲ��洢�����������������ʵ�֡�����������£�����˫��ȡ������ʱ������FFT��ʱ��ƽ��������49.3 %�������ﵽ���������������һ�롣�����ĺ����һ��ʱ������FFT��ʱ��ƽ��������72.5%�������ð˺�ʱƽ������ʱ���������81.6%��

����һ��FFT�ֱ���1/2/4/8DSP��ʱ���ڼ�����Ľ��

�ɴ����ǿ��Կ�����������˫�˻����ĺˣ�����FFT�Ĵ�С��16k���ӵ�256k������ʱ����ٵķ���ҲԽ��Խ�����ð˺�ʱ����ʱ����ٵķ��ȸ��Ӿ��ҡ�������Ϊ���ڽ�С��FFT������Խ�࣬���д�������ڶ������Ӻ�����������ܵĴ���ҪС�ܶࡣ��ǰ256KB��FFT����������ܷ����Ч������̫���룬��˫��ʱֻ�����2�����ĺ�ʱҲֻ��4�������ڰ˺�ʱ�����ή�������ܡ��������ڰ˺˴������ݵ��ٶ�Զ�����ⲿ�洢���������ݵ��ٶȣ��Ӷ�ʹ��洢�ռ䵽�������µġ��ڱ���ʾ�У�����һ����СΪ1024k��FFT����һ������FFT���ڲ���8 ��DSP�ںˣ���������Ϊ1GHzʱ������ʱ���6.4���롣

ͼ�������������������ϵ�����

����

������������TI��TMS320C6678��������ִ��һ��������FFT����1GHz�Ĺ���Ƶ���£�8��ͬʱ��������ʱ�����6.4���롣��˸��ٵ�DSP�ں���ȫ��������ִ��ijЩӦ�õ�ʵʱ���㣬�����״����ս����ҽѧ��ͼ�ȡ�����ýϴ��ٶ�1.25GHz������TMS320C6678��������ͬʱ���ø��ߴ�����DDR3��1600MTPS�Ļ���ִ����������ʱ�����̡�

����Ķ�:

- ...2013/02/19 10:01��StreamWIDE�Ƴ�����Ӫ��Ϊ�������ƶ�ͨѶ��ȫ�±���SmartMS™����

- ...2012/10/12 10:28�������������� Hercules™ TMS570 ARM® ��ȫ����������Դ�������ɵ�· (PMIC) �͵��������Ϊ��������ͨ�������ʵ�ֿ�Խʽ��

- ...2012/08/13 12:45�������������µͳɱ� TMS320C665x KeyStone ��� DSP Ϊ��ҵ���ؿ�����Ա�ṩ���ߵ��ܶ������չ��

- ...2011/11/22 10:59����������(TI)�Ƴ� TMS320C66x ��� DSP ��Ʒ

- ...2011/10/24 16:28�����������Ƴ����� TMS320C66x DSP ��������������� �������������ҽ��Ӱ����Ա�Գ��������볬��Ӱ������������

- ...2011/10/21 14:16����ǿ��ĵ������� TMS320C66x ��� DSP Э����ҵ�Զ���������Աʵ�����ܡ�����չ�Լ�����ԵĿ�ǰ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����