����ADV7125��Ƕ��ʽϵͳVGA�ӿ����

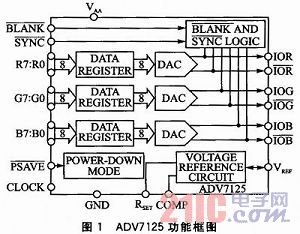

����ADV7125��3����Ƶ���ݼĴ���DATA REGISTER��һ����Ƶ���ƼĴ���POWER-DOWN MODE�����ݼĴ�����3������˷ֱ����Ӻ�������ɫ��������Ƶ�źţ����ݼĴ������������ģת����Ԫ���������ź�ת��Ϊģ���źţ����ƼĴ��������ֵ������źš�ͬ���ź�ת���ϲ�����ģת�����ģ����Ƶ�źźͿ��ƼĴ��������ͬ�������������źŹ�ͬ��ΪADV7125������źţ�������źŴ�С��Rset�˺͵�֮��������ӵ���RSET��С�Ŀ��ơ�

����2 ADV7125оƬ����VGAת���Ļ���ԭ��

����ADV7125оƬ����VGAת���Ļ���ԭ���ǣ���S3C2440�����������Ƶ�ź�ת��Ϊģ���VGA����źţ�ģ���VGA����źŵĴ�С��ADV71 25оƬ��Χ�ο���ѹVREF����ӵ���RSET�Ŀ��ƣ�(VREF��RSET�ľ���ӷ���ͼ4��ʾ)���ϵ���£�

![]()

����ʽ��IOG��IOR��IOB�ֱ�����̡��졢����ɫ�źŵķ��ȡ������ø���ͬ���ź�![]() ʱ����Ҫ��

ʱ����Ҫ��![]() �����ӵ͵�ƽ����ʱIOG�Ĺ�ϵʽͬʽ(2)��

�����ӵ͵�ƽ����ʱIOG�Ĺ�ϵʽͬʽ(2)��

������ʽ�е�![]() ��ADV7125��һ�������źſ��ƶˣ�ADV7125������һ�������źſ��ƶ���

��ADV7125��һ�������źſ��ƶˣ�ADV7125������һ�������źſ��ƶ���![]() (�����źſ��ƶ�)��

(�����źſ��ƶ�)��![]() ��

��![]() ������ʱ�������ر����棬��֤������������ͬ����

������ʱ�������ر����棬��֤������������ͬ����![]() ��

��![]() �Ĺ����ǣ�ͨ����Ƶͬ���źŵı��룬Ӱ��VGA��Ƶ�źŵ������ͨ����ģ������˿��ڲ�����һ����Ȩ������ʵ�ִ˹��ܡ�������������ޣ���

�Ĺ����ǣ�ͨ����Ƶͬ���źŵı��룬Ӱ��VGA��Ƶ�źŵ������ͨ����ģ������˿��ڲ�����һ����Ȩ������ʵ�ִ˹��ܡ�������������ޣ���![]() ��

��![]() ���������

���������

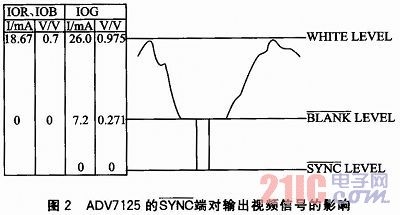

����ͼ2˵���˵�![]() ��

��![]() ���߶�Ϊ�ߵ�ƽʱ��IOR��IOB������IOG�ĶԱȡ�

���߶�Ϊ�ߵ�ƽʱ��IOR��IOB������IOG�ĶԱȡ�

������1��ϸ˵����![]() ��

��![]() ��ģ�������Ӱ�졣�ñ�����VREF=1��235 V��RSET=530 Ω��RLOAD=37��5Ω�������²����ġ�

��ģ�������Ӱ�졣�ñ�����VREF=1��235 V��RSET=530 Ω��RLOAD=37��5Ω�������²����ġ�

������Ӧͼ2�ͱ�1�ɵõ����½��ۣ�

�����ٵ�IOR��IOG��IOB���˵�DAC����Ϊ0x00ʱ��������Ļ�Ϻڣ���ʱ��Ӧͼ2Ϊ![]() LEVEL����Ӧ��1Ϊ��7�С���ͼ2�����б����Կ�����IOR��IOB�˵ĵ�������ѹ�ֱ���0mA��0V��IOG�˵ĵ�������ѹ�ֱ���7��2 mA��0��271 V�����������7��2 mA��

LEVEL����Ӧ��1Ϊ��7�С���ͼ2�����б����Կ�����IOR��IOB�˵ĵ�������ѹ�ֱ���0mA��0V��IOG�˵ĵ�������ѹ�ֱ���7��2 mA��0��271 V�����������7��2 mA��

�����ڵ�IOR��IOG��IOB���˵�DAC����Ϊ0xFFʱ��������Ļ�ϰף���ʱ��Ӧͼ2ΪWHITE LEVEI����Ӧ��1Ϊ��2�С���ͼ2�����б����Կ�����IOR��IOB�˵ĵ�������ѹ�ֱ���18��67 mA��0��7 V��IOG�˵ĵ�������ѹ�ֱ���26��0 mA��0��975 V�����������7��3 mA��

�����ӱ�1�����Եõ����µĽ��ۣ�

�����ٵ�![]() ��

��![]() ��Ϊ�ߵ�ƽ(Ϊ1)ʱ��IOG�˿ڵİ�ƽ�źŵĵ�����Ҫ��IOR��IOB�˿�ͬ������µĵ����߳�7��3mA���ң���Ƶ�źŵ������ڵ�ƽ�źŵĵ�����Ҫ��IOR��IOB�˿�ͬ������µĵ����߳�7��2 mA���ҡ�

��Ϊ�ߵ�ƽ(Ϊ1)ʱ��IOG�˿ڵİ�ƽ�źŵĵ�����Ҫ��IOR��IOB�˿�ͬ������µĵ����߳�7��3mA���ң���Ƶ�źŵ������ڵ�ƽ�źŵĵ�����Ҫ��IOR��IOB�˿�ͬ������µĵ����߳�7��2 mA���ҡ�

�����ڵ�![]() Ϊ�͵�ƽ(Ϊ0)��

Ϊ�͵�ƽ(Ϊ0)��![]() ����ʱ��ͬ����DAC���������£�IOR��IOB��IOG���˵�����źŵ�����С����ȫһ���ġ�

����ʱ��ͬ����DAC���������£�IOR��IOB��IOG���˵�����źŵ�����С����ȫһ���ġ�

�����۵�![]() Ϊ�͵�ƽ(Ϊ0)ʱ������DAC�����Ƕ��٣�IOR��IOG��IOB���˵�����źž���Ӧ��

Ϊ�͵�ƽ(Ϊ0)ʱ������DAC�����Ƕ��٣�IOR��IOG��IOB���˵�����źž���Ӧ��![]() �ߣ��͵�ͬ����Ч����Ч�ڵ�ƽ��

�ߣ��͵�ͬ����Ч����Ч�ڵ�ƽ��

����3 VGA�ӿ����

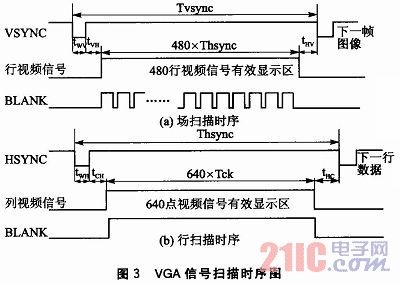

����������Ҫ����LCD�ź�ת��ΪVGA�źţ�ת��ʱ�������VGA�źŵ�ʱ�����ת����VGA�ź�һ������5���֣��ֱ��Ǻ�(R)����(G)����(B)��ɫ�źź���(H)����(V)ͬ���źţ���(R)����(G)����(B)��ɫ�źź���(H)����(V)ͬ���źŸ���S3C2440������ʱ����S3C2440�������źŵ���ʽ�����֮����ADV7125�Ժ�(R)����(G)����(B)��ɫ�źŽ���ת������(H)����(V)ͬ���ź�ֱ�ӽ���VGA�ӿ��У�����Ҫת��������ֱ����VGA�źŵ�ʱ��Ӳ�����ӡ���������Լ�ע�����

����3��1 VGAʱ���ź�

�����Էֱ���Ϊ640x480��ˢ��Ƶ��Ϊ60 Hz��16λ�IJ�ɫ��ʾģʽΪ����VGA�źŵ�ɨ��ʱ����ͼ3��ʾ��

�����ڳ�ɨ��ʱ���У�VSYNCΪ��ͬ���źţ�Tvsync��ָ��ʾ��ɨ��1֡����������Ҫ��ʱ�䣬��СΪ16 667μs��VSYNC�ź�ÿ����525�У�����480��Ϊ��Ч��ʾ�У�45���dz������ڡ��������ڰ�����ͬ��ʱ��(�͵�ƽ��ͬ������)twv(2�У�63μs)��������ǰ��tHV(13�У�412μs)�����������tVH(30�У�952 μs)����45�С�

��������ɨ��ʱ���У�HSYNCΪ��ͬ���źţ�Thsync��ָ��ʾ��ɨ��һ����Ҫ��ʱ�䣬��СΪ31��75μs��������ͨ��Hsync(��ͬ������)��ͬ��������Ŀ���tWH=3��81μs��ÿ��ʾ�а���800�㣬����640��Ϊ��Ч��ʾ����160��Ϊ��������(�Ƿ���ʾ��)���������ڰ�����ͬ��ʱ��tWH(3��81μs)��������ǰ��tHC(0��516μS)�����������tCH(1��786μs)����160����ʱ�ӡ�

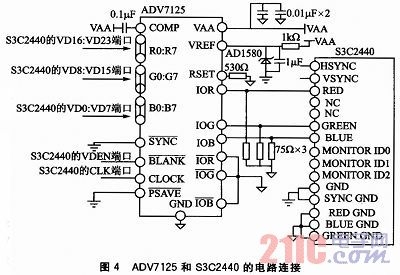

����3��2 S3C2440��ADV7125�ĵ�·����

�����������Ҫʹ��S3C2440��������LCD�������ӿڣ�����Ҫͨ��DMA��ʽռ��ϵͳ���ߣ�֧�ֲ�ɫTFTҺ������֧��16 bbp��ɫ��ʡ�LCD�ӿ����ݵĵ�8λ���м�8λ��8λ�ֱ���ADV7125оƬ��BLUE�źš�GREEN�źź�RED�ź������������������S3C2440��������ADV7125оƬ֮�������źŵĴ��䡣ADV7125оƬ��ʱ���źŲ���LCD�ӿڵ�ʱ���źţ�![]() �ź���VM(VSDN)�ź������ӣ�

�ź���VM(VSDN)�ź������ӣ�![]() ͬ���źŽӵء�COMP�������ڲ��ο��˷ŵIJ�������0��1μF���մɵ���������COMP��ģ���ԴVAA֮�䣬��ֹ�Լ����������ȶ��ԡ�����AD1580��Ϊ�ο���ѹ��AD1580����ź��ȶ����ܹ��ܺõ������·��Ƶ���Ҫ��RSET�������֮���һ��530 Ω�ĵ��裬����������Ƶ�źŵ������ȡ���ͼ��ϵͳ�У������Զ���������ͬ���ź�

ͬ���źŽӵء�COMP�������ڲ��ο��˷ŵIJ�������0��1μF���մɵ���������COMP��ģ���ԴVAA֮�䣬��ֹ�Լ����������ȶ��ԡ�����AD1580��Ϊ�ο���ѹ��AD1580����ź��ȶ����ܹ��ܺõ������·��Ƶ���Ҫ��RSET�������֮���һ��530 Ω�ĵ��裬����������Ƶ�źŵ������ȡ���ͼ��ϵͳ�У������Զ���������ͬ���ź�![]() �����ñ���ƿ���ʵ����Ƶͬ����Ϣ����ֱ�ӽ�����ɫ�ŵ����������Ҫ����

�����ñ���ƿ���ʵ����Ƶͬ����Ϣ����ֱ�ӽ�����ɫ�ŵ����������Ҫ����![]() ����������͵�ƽ������S3C2440��ADV7125�ĵ�·������ͼ4��ʾ������VD0��VD1��…VD23��VDEN��CLK��HSYNC��VSYNCΪS3C2440������ˡ� ����

����������͵�ƽ������S3C2440��ADV7125�ĵ�·������ͼ4��ʾ������VD0��VD1��…VD23��VDEN��CLK��HSYNC��VSYNCΪS3C2440������ˡ� ����

����3��3 ��·������Ҫע�������

����ADV7125�������ڻҶ���Ƶ�ź��������

����Ķ�:

- ...2013/10/16 13:40������AXIe �� PCIe �ߴ�������ģ��ͬ�����ݴ���ĸ���ͼ�δ���ϵͳ

- ...2012/04/23 12:15������AVR��Ƭ������Ƶ��Դ����ϵͳ

- ...2012/03/31 14:49��ʵ�ֻ���ARM��Ƕ��ʽϵͳ��SoC����

- ...2012/03/22 11:18�����ڣ��Σƣɣӵĺ��ײɿ����߿���

- ...2012/03/20 14:53�����ڣ��ģӪ��µķɻ�Ԥ����ײ�㷨�о�

- ...2012/03/14 14:36������ARM�������ĵ�Ŀ�Ӿ���ඨλϵͳ

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...�� ���ݲɼ��ն�ϵͳ�豸

- ...�� ���ǿƼ�̤��������

- ...�� ����˼® ���� AEC-Q100 ������֤������ϵ�в�Ʒ�ƻ�

- ...�� ����˼® ������������� �ѽ�ϵ��™ FPGA ��Ʒ �ѽ�ϵ�в�Ʒ���������� 1M ����Ԫ�� FPGA

- ...�� ����˼® ����Trion® Titanium ��̨���� (TSMC) 16�����սڵ���Ƭ

- ...�� TI��2019��ȫ����ѧ��������ƾ����佱�����ھ�����

- ...�� BlackBerry QNX��������ȫ����������ȫ�����Եȼ�(ASIL) ��D����֤

- ...�� ��������ѡ��BlackBerry������һ������